SN8P2711A

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD

Page 3

Version 0.1

Table of Content

AMENDENT

HISTORY................................................................................................................................ 2

1

1

1

PRODUCT OVERVIEW................................................................................................................. 7

1.1 FEATURES ........................................................................................................................................ 7

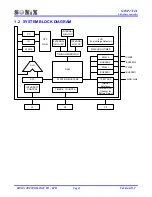

1.2 SYSTEM

BLOCK

DIAGRAM .......................................................................................................... 9

1.3 PIN

ASSIGNMENT ......................................................................................................................... 10

1.4 PIN

DESCRIPTIONS....................................................................................................................... 11

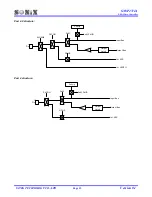

1.5 PIN

CIRCUIT

DIAGRAMS............................................................................................................. 12

2

2

2

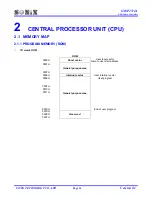

CENTRAL PROCESSOR UNIT (CPU) ...................................................................................... 14

2.1 MEMORY

MAP............................................................................................................................... 14

2.1.1 PROGRAM

MEMORY

(ROM)............................................................................................... 14

2.1.1.1 RESET

VECTOR

(0000H) .................................................................................................. 15

2.1.1.2 INTERRUPT

VECTOR

(0008H)......................................................................................... 16

2.1.1.3

LOOK-UP TABLE DESCRIPTION.................................................................................... 18

2.1.1.4

JUMP TABLE DESCRIPTION ........................................................................................... 20

2.1.1.5 CHECKSUM

CALCULATION........................................................................................... 22

2.1.2 CODE

OPTION

TABLE.......................................................................................................... 23

2.1.3

DATA MEMORY (RAM) ....................................................................................................... 24

2.1.4 SYSTEM

REGISTER .............................................................................................................. 25

2.1.4.1

SYSTEM REGISTER TABLE ............................................................................................ 25

2.1.4.2 SYSTEM

REGISTER

DESCRIPTION ............................................................................... 25

2.1.4.3

BIT DEFINITION of SYSTEM REGISTER....................................................................... 26

2.1.4.4 ACCUMULATOR ............................................................................................................... 27

2.1.4.5 PROGRAM

FLAG ............................................................................................................... 28

2.1.4.6 PROGRAM

COUNTER....................................................................................................... 29

2.1.4.7

Y, Z REGISTERS................................................................................................................. 32

2.1.4.8 R

REGISTERS ..................................................................................................................... 33

2.2 ADDRESSING

MODE .................................................................................................................... 34

2.2.1

IMMEDIATE ADDRESSING MODE .................................................................................... 34

2.2.2

DIRECTLY ADDRESSING MODE ....................................................................................... 34

2.2.3 INDIRECTLY

ADDRESSING MODE ................................................................................... 34

2.3 STACK

OPERATION...................................................................................................................... 35

2.3.1 OVERVIEW............................................................................................................................. 35

2.3.2 STACK

REGISTERS............................................................................................................... 36

2.3.3 STACK

OPERATION

EXAMPLE.......................................................................................... 37

3

3

3

RESET ............................................................................................................................................. 38