SN8P2711A

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD

Page 43

Version 0.1

LVD Code Option

LVD

LVD_L

LVD_M

LVD_H

2.0V Reset

Available

Available

Available

2.4V Flag

-

Available

-

2.4V Reset

-

-

Available

3.6V Flag

-

-

Available

LVD_L

If VDD < 2.0V, system will be reset.

Disable LVD24 and LVD36 bit of PFLAG register.

LVD_M

If VDD < 2.0V, system will be reset.

Enable LVD24 bit of PFLAG register. If VDD > 2.4V, LVD24 is “0”. If VDD <= 2.4V, LVD24 flag is “1”.

Disable LVD36 bit of PFLAG register.

LVD2_H

If VDD < 2.4V, system will be reset.

Enable LVD24 bit of PFLAG register. If VDD > 2.4V, LVD24 is “0”. If VDD <= 2.4V, LVD24 flag is “1”.

Enable LVD36 bit of PFLAG register. If VDD > 3.6V, LVD36 is “0”. If VDD <= 3.6V, LVD36 flag is “1”.

Note:

1. After any LVD reset, LVD24, LVD36 flags are cleared.

2. The voltage level of LVD 2.4V or 3.6V is for design reference only. Don’t use the LVD indicator

as precision VDD measurement.

Watchdog reset:

The watchdog timer is a protection to make sure the system executes well. Normally the watchdog timer would be clear

at one point of program. Don’t clear the watchdog timer in several addresses. The system executes normally and the

watchdog won’t reset system. When the system is under dead-band and the execution error, the watchdog timer can’t

be clear by program. The watchdog is continuously counting until overflow occurrence. The overflow signal of

watchdog timer triggers the system to reset, and the system return to normal mode after reset sequence. This method

also can improve brown out reset condition and make sure the system to return normal mode.

If the system reset by watchdog and the power is still in dead-band, the system reset sequence won’t be successful

and the system stays in reset status until the power return to normal range. Watchdog timer application note is as

following.

Reduce the system executing rate:

If the system rate is fast and the dead-band exists, to reduce the system executing rate can improve the dead-band.

The lower system rate is with lower minimum operating voltage. Select the power voltage that’s no dead-band issue

and find out the mapping system rate. Adjust the system rate to the value and the system exits the dead-band issue.

This way needs to modify whole program timing to fit the application requirement.

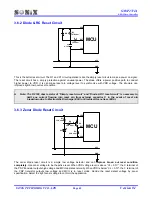

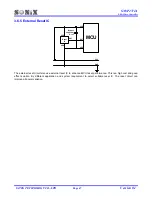

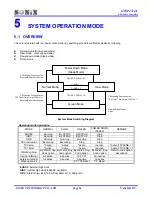

External reset circuit:

The external reset methods also can improve brown out reset and is the complete solution. There are three external

reset circuits to improve brown out reset including “Zener diode reset circuit”, “Voltage bias reset circuit” and “External

reset IC”. These three reset structures use external reset signal and control to make sure the MCU be reset under

power dropping and under dead-band. The external reset information is described in the next section.