SN8P2711A

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD

Page 61

Version 0.1

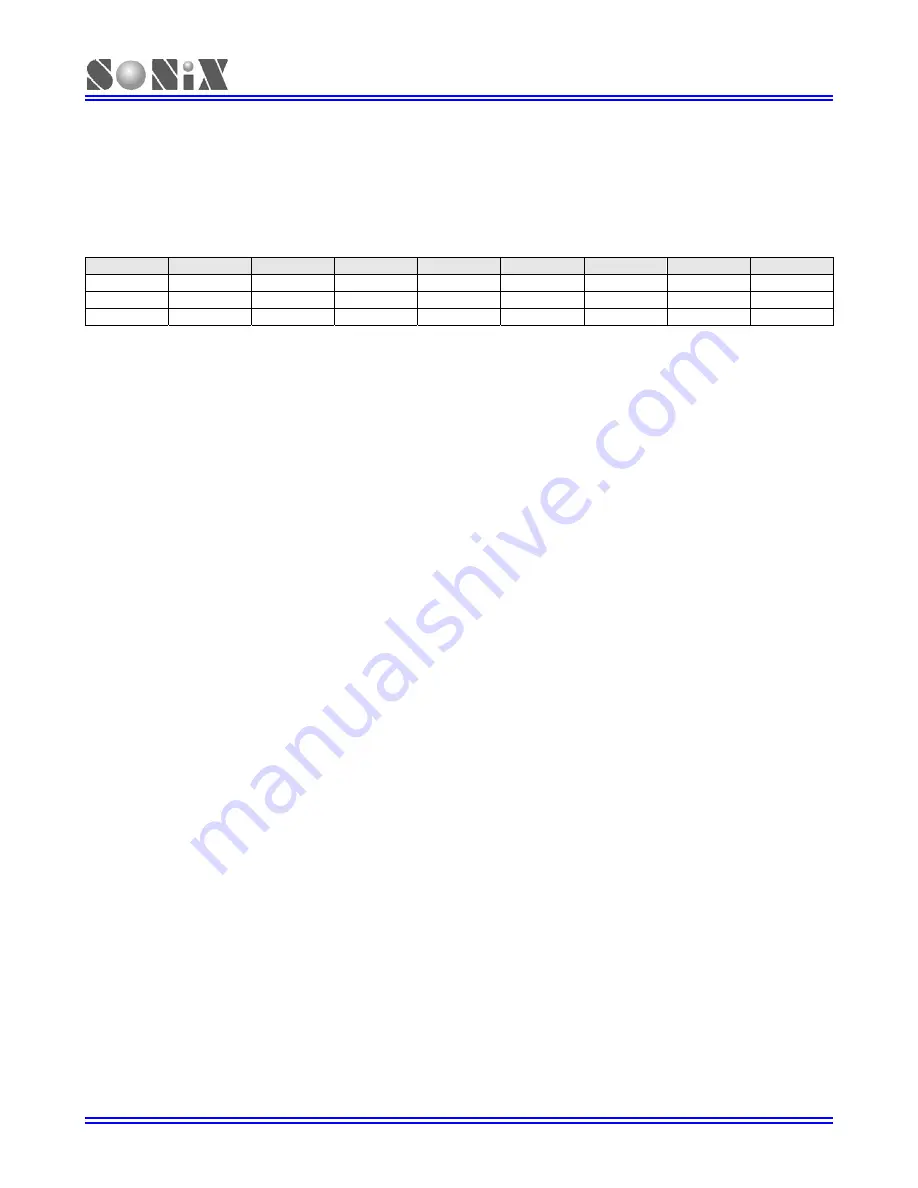

6.2 INTEN INTERRUPT ENABLE REGISTER

INTEN is the interrupt request control register including three internal interrupts, two external interrupts enable control

bits. One of the register to be set “1” is to enable the interrupt request function. Once of the interrupt occur, the stack is

incremented and program jump to ORG 8 to execute interrupt service routines. The program exits the interrupt service

routine when the returning interrupt service routine instruction (RETI) is executed.

0C9H

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

INTEN

ADCIEN TC1IEN TC0IEN

- - -

P01IEN

P00IEN

Read/Write

R/W R/W R/W -

-

- R/W R/W

After

reset

0 0 0 - - - 0 0

Bit 0

P00IEN:

External P0.0 interrupt (INT0) control bit.

0 = Disable INT0 interrupt function.

1 = Enable INT0 interrupt function.

Bit 1

P01IEN:

External P0.1 interrupt (INT1) control bit.

0 = Disable INT1 interrupt function.

1 = Enable INT1 interrupt function.

Bit 5

TC0IEN:

TC0 timer interrupt control bit.

0 = Disable TC0 interrupt function.

1 = Enable TC0 interrupt function.

Bit 6

TC1IEN:

TC1 timer interrupt control bit.

0 = Disable TC1 interrupt function.

1 = Enable TC1 interrupt function.

Bit 7

ADCIEN:

ADC interrupt control bit.

0 = Disable ADC interrupt function.

1 = Enable ADC interrupt function.