C702

1221-7857 rev. 1

APPENDIX

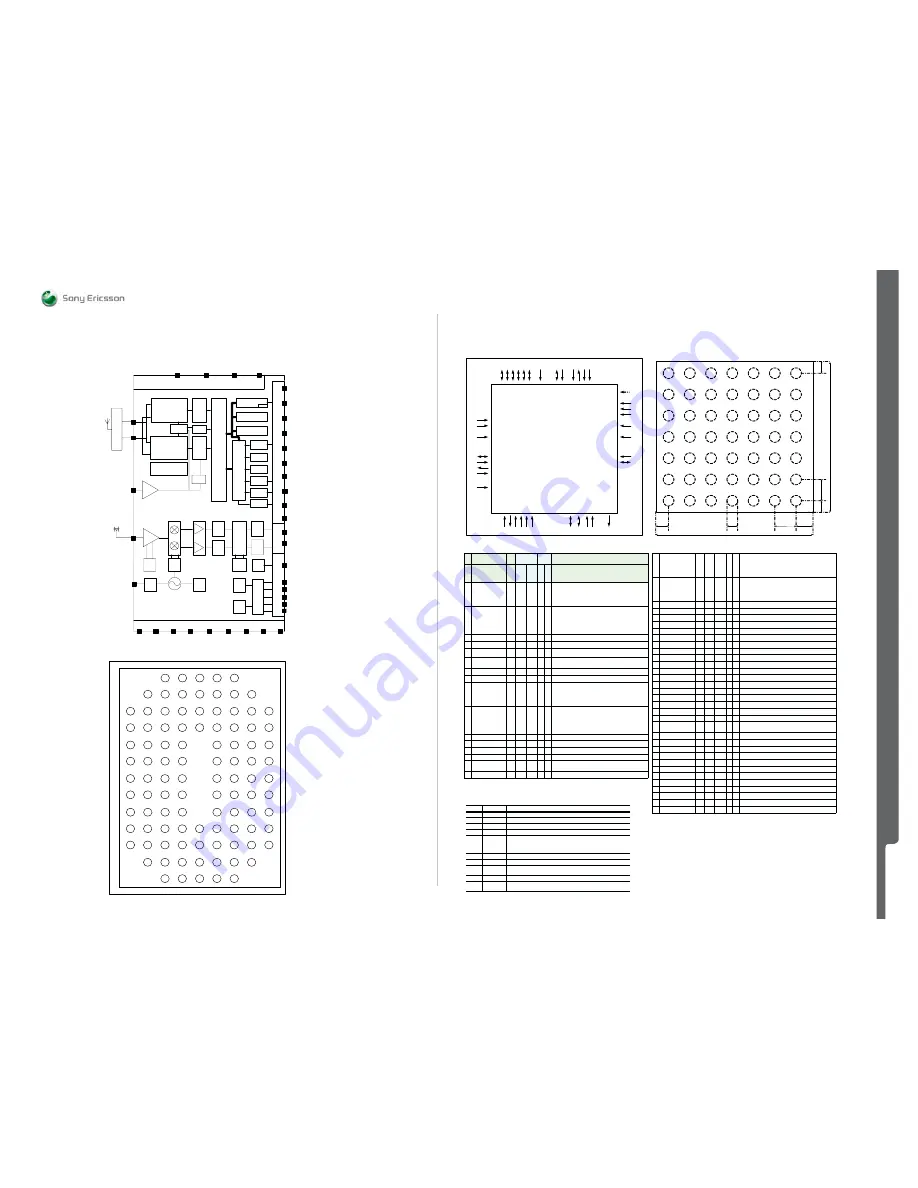

Components - N1400, N1430

A

P

P

E

NDIX

N1400 Module Blu FM Radio STLC2592 1200-6182

BLOCK DIAGRAM AND ELECTRICAL SCHEMATIC

F

I

L

T

E

R

RECEIVER

TRANSMITTER

RF PLL

Fractional N

DEMOD

MOD

BASEBAND

CORE EBC

CONTROL

AND

REGISTER

AUTOCALIBRATION

PLL

AMBA

PERIOH .

BUS

TIMER

UART / SPI

INTERRUPT

PCM

RAM

ARM7TDMI

CPU Wrapper

WLAN

I2C

ROM

JTAG

LNA

VGA

I

ADC

Q

ADC

DSP

FILTER

DEMOD

MPX

AUDIO

DAC

DAC

AGC

0 / 90

LOW-IF

GPIO

TUNE

AFC

RDS

RSSI

CO

NT

RO

L

IN

TE

R

FA

C

E

BT_RFP

BT_RFN

BT _REF_CLK_IN

FM_FMIP

FM_RCLK

]

0

:

4

[

O

I

V

_

T

B

]

0

:

5

[

V

H

_

T

B

D

V

_

M

F

A

V

_

M

F

BT_GPIO

[5:0]

BT_LP_CLK

BT_HOST_WAKEUP/

BT_SPI_INT

BT _WAKEUP

BT _RESETN

BT_UART/

BT _SPI [3:0]

BT_PCM

[3:0]

BT_CONFIG

[2:0]

BT_CLK_REQ_IN

[1:0]

BT_CLK_REQ_OUT

[1:0]

FM_LOUT

FM_ROUT

FM_GPIO

[2:0]

FM_VIO

FM_RSTB

FM_SDIO

FM_SCLK

FM_SENB

NC

[5:0]

BT_REG_

CTRL

FM_GND

[7:0]

BT _RSRV

[4:0]

FM_RFGND

BT_TEST

[1:0]

BT_VDD_CLD

BT _AF_PRG

BT_VSS

[20:0]

Headphone

Cable

Pinout Bottom View

A

B

C

D

E

F

G

H

J

K

L

M

N

FM_GND

FM_VA

FM_GPIO3

FM_GPIO2

FM_GPIO1

FM_VD

FM_GND

FM_LOUT

FM_GND

FM_GND

BT_RSRV_CL

FM_FMIP

BT_RSRV_N

BT_RSRV_CL

FM_GND

FM_ROUT

FM_GND

BT_RSRV_DSM

FM_GND

FM_RFGND

FM_RSTB

BT_VSSANA

BT_HVA

NC

FM_GND

FM_VIO

BT_VSSANA

FM_RCLK

FM_SDIO

FM_SENB

BT_HVA

BT_VSSANA

BT_HVA

BT_VDD_CLD

BT_HVA

BT_CLK_

REQ_IN1

BT_HOST_WAKEUP

BT_SPI_INT

FM_SCLK

BT_VSSANA

BT_VSSANA

BT_VSSANA

BT_REF_CLK_IN

BT_VSSANA

NC

NC

BT_CLK_REQ_IN2

BT_TEST2

BT_VSSANA

BT_VSSANA

BT_AF_PRG

BT_VSSANA

BT_UART_TXD

BT_SPI_DO

BT_VIO_E

BT_GPIO_0

BT_TEST1

BT_VSSANA

BT_VSSANA

BT_VSSDIG

BT_VSSRF

BT_VSSDIG

BT_VSSDIG

BT_UART_RXD

BT_SPI_DI

BT_VSSRF

BT_GPIO_16 BT_REG_CTRL

BT_UART_RTS

BT_SPI_CSN

BT_RFN

BT_CLK_

REQ_OUT1

BT_CLK_

REQ_OUT2

BT_VIO_B

BT_VSSRF

BT_GPIO_11

BT_GPIO_10

BT_PCM_A

BT_UART_CTS

BT_SPI_CLK

BT_RFP

BT_RESETN

BT_VSSDIG

BT_LP_CLK

BT_HVA

BT_GPIO_8

NC

NC

NC

BT_VSSRF

BT_CONFIG_1

BT_VSSDIG

BT_WAKEUP

BT_GPIO_9

BT_PCM_CLK

BT_PCM_B

BT_VIO_A

BT_CONFIG_2

BT_RSRV_RF

BT_RSRV_D

BT_PCM_SYNC

BT_VIO_D

BT_CONFIG_3

BT_HVD

BT_VIO_C

1

2

3

4

6

7

8

9

5

N1430 IC A-GPS Hammerhead 2 1200-0700

VDD_PLL

VDD_LP_PLLREG_IN

VDD_LPREG_OUT

VDD_LP

Cl

o

ck

&

S

ync

hr

on

iz

a

ti

o

n

CLK

SYNC

CNTIN

VDD_IO

LP

a

nd

P

L

L

S

u

pp

ly

Core

Supply

Multiplexed

Serial Interface

HI

F

4

HI

F

5

System

Integration

Op

e

ra

ti

o

n

a

l

Mo

d

e

OMS2

OMS1

OMS0

RT

C

C

L

K

nI

N

T

R

PO

W

E

R

O

N

RX

_

H

O

L

D

V

D

D_

CO

RE

R

EG

_

O

U

T

V

D

D_

CO

R

ER

E

G

_I

N

HI

F

3

HI

F

2

HI

F

1

HI

F

0

VD

D

_

IO

VD

D

_

C

O

R

E

JTAG Interface

TD

I

TD

O

TM

S

TC

K

nT

R

ST

VDD_CORE

nRESET

Hammerhead II

(SG-UFWLB-49 )

VDD_CORE

EX

T

_

LN

A

_

C

T

R

L

VDD_RFREG_IN

VDD_RF

RF

S

u

p

p

ly

MI

X

_

IN

_

P

LU

S

MI

X

_

IN

_

M

IN

US

VCO Mixer

VD

D

_

VC

O

VD

D

_

C

A

P

Decouple

EXT_LNA

Top view (PCB footprint)

B1

C1

D1

E1

F1

G1

A2

B2

C2

D2

E2

F2

G2

A3

B3

C3

D3

E3

F3

G3

A4

B4

C4

D4

E4

F4

G4

A5

B5

C5

D5

E5

F5

G5

A6

B6

C6

D6

E6

F6

G6

A7

B7

C7

D7

E7

F7

G7

0.5 mm

0.

5

mm

3.7 mm

3.5

5

m

m

0.25

mm

0.4 mm

A1

0.3

mm

0.

275

mm

0.

27

5

mm

Pin

No.

Pin

Name

Pad

Type

Pad

Usage

O/P

State

Direc

tion

Addi

ti

onal

Rese

t

Standb

y

Pad Functional Description

A1 HIF3

UART_RXD /

UART_RXD /

I

2

C_GROUP1 /

SPI_nSCS

I/O

I

(I)

I

I

-

-

-

-

-

-

-

-

-

-

-

-

Host Interface

OMS[2:0]=[1,1,1]: UART Interface: Data Input

OMS[2:0]=[1,1,0]: UART Interface: Data Input (Ignored)

OMS[2:0]=[1,0,1]: Selection of I

2 C group address

OMS[2:0]=[1,0,0]: SPI chip select

A2 HIF4

UART_nRTS /

UART_nRTS /

I

2

C_A0 /

SPI_SI

I/O

O

Z

I

I

-

-

-

-

0

Z

-

-

0

Z

-

-

Host Interface

OMS[2:0]=[1,1,1]: UART Interface: hardware flow control

OMS[2:0]=[1,1,0]: UART Interface: hardware flow control

(Tristated)

OMS[2:0]=[1,0,1]: Selection of I

2 C group address bit 0

OMS[2:0]=[1,0,0]: SPI serial data input

A3 CNTIN

I

I

-

-

-

Digital high accuracy frequency reference

A4 CLK

I/AI

I

-

-

-

Clock signal input. Selectable as digital or analog input

A5 VDD_PLL

PI/

PO

-

-

-

-

Digital PLL supply Decoupling

A6 VDD_LP_PLLREG_I

N

PI

-

-

-

-

PLL voltage and Low Power core regulator input

A7 VDD_IO

PI

-

-

-

-

Digital I/O supply

B1 VSS_DIG

GND -

-

-

-

B2 HIF2

UART_TXD /

UART_TXD /

I

2

C_GROUP0 /

SPI_SCK

I/O

O

Z

I

I

-

-

-

-

0

Z

-

-

0

Z

-

-

Host Interface

OMS[2:0]=[1,1,1]: UART Interface: Data Output

OMS[2:0]=[1,1,0]: UART Interface: Data Output (Tristated)

OMS[2:0]=[1,0,1]: Selection of I

2 C group address

OMS[2:0]=[1,0,0]: SPI clock

B3 HIF5

UART_nCTS /

UART_nCTS /

- /

SPI_SO

I/O

-

I

(I)

I

O/Z

-

-

-

-

-

-

-

-

-

Z

-

-

-

-

Z

Host Interface

OMS[2:0]=[1,1,1]: UART Interface: hardware flow control

OMS[2:0]=[1,1,0]: UART Interface: hardware flow control

(Ignored)

OMS[2:0]=[1,0,1]: not used (tie to “0”)

OMS[2:0]=[1,0,0]: SPI serial data output

B4 VDD_LPREG_OUT

PO

-

-

-

-

Low Power core regulator output

B5 TDI

I/O

I

PU “C” 1

1

Serial Data Input (JTAG, IEEE 1149.1)

B6 VDD_LP

PI

-

-

-

-

Low Power supply

B7 VDD_CORE

PI

-

-

-

-

Digital core supply

C1 VDD_COREREG_O

UT

PO

-

-

-

-

Digital core voltage regulator output

C2 VDD_IO

PI

-

-

-

-

Digital I/O supply

C3 HIF0

- /

- /

I

2

C_SCL /

-

I/O

I

I

I

2

C I

I

-

-

-

-

-

-

-

-

-

-

-

-

Host Interface

OMS[2:0]=[1,1,1]: not used (tie to “0”)

OMS[2:0]=[1,1,0]: not used (tie to “0”)

OMS[2:0]=[1,0,1]: I

2 C clock

OMS[2:0]=[1,0,0]: not used (tie to “0”)

C4 HIF1

- /

- /

I

2

C_SDA /

-

I/O

I

I

I

2

C I/O

I

-

-

OD

-

-

-

Z

-

-

-

Z

-

Host Interface

OMS[2:0]=[1,1,1]: not used (tie to “0”)

OMS[2:0]=[1,1,0]: not used (tie to “0”)

OMS[2:0]=[1,0,1]: I

2 C data

OMS[2:0]=[1,0,0]: not used (tie to “0”)

C5 TDO

I/O

O

-

Z

Z

Serial Data Output (JTAG, IEEE 1149.1)

C6 TCK

I/O

I

PD “C” 0

0

Clock (JTAG, IEEE 1149.1)

C7 nTRST

I/O

I

PD “A” 0

0

Reset Input (JTAG, IEEE 1149.1)

D1 VDD_COREREG_IN

PI

-

-

-

-

Digital core voltage regulator supply

D2 VSS_DIG

GND -

-

-

-

D3 OMS1

I/O

I

-

-

-

Operational mode select / Bus interface select

D4 SYNC

I

I

-

-

-

Digital reference time pulse

D5 VSS_DIG

GND -

-

-

-

D6 TMS

I/O

I

PU “C” 1

1

State Machine Control Signal (JTAG, IEEE 1149.1)

D7 VSS_DIG

GND -

-

-

-

E1 RTCCLK

I/O

I

Hyst

-

-

32.768kHz clock signal input

E2 POWERON

I/O

I

-

0

0

Power On signal to chip

E3 OMS0

I/O

I

-

-

-

Operational mode select / Bus interface select

E4 VSS_LNA

GND -

-

-

-

E5 VSS_RF

GND -

-

-

-

E6 MIX_IN_PLUS

AI

AI

-

-

-

Differential mixer input

E7 VDD_CAP

PI/O PI/O

-

(Z) (Z)

RF Digital Supply Decoupling

F1 nINTR

I/O

O

OD

Z

Z

Interrupt request signal to host

F2

RX_HOLD

I/O

I

-

-

-

RX_HOLD signal (From host to indicate that the host is

transmitting)

F3 nRESET

I/O

I

Hyst

0

1

Chip reset signal

F4 VDD_RFREG_IN

PI

-

-

-

-

RF voltage regulator input

F5 EXT_LNA_CTRL0

AI/O O

-

-

-

External LNA control

F6 MIX_IN_MINUS

AI

AI

-

-

-

Differential mixer input

F7 VDD_VCO

PI/O PI/O

-

(Z) (Z)

Buffer capacito r for VCO supply

G1 VDD_CORE

PI

-

-

-

-

Digital core supply

G2 OMS2

I/O

I

-

-

-

Operational mode select

G3 VDD_CORE

PI

-

-

-

-

Digital core supply

G4 VSS_RF

GND -

-

-

-

G5 VDD_RF

PI/0

-

-

-

-

RF Analog Supply Decoupling

G6 VSS

AI

AI

-

-

-

G7 N.C.

AO

AO

-

-

-

This ball should be left unconnected

GND

Chip Ground

All signals are referred to this

P I

Power In

Supply to a voltage domain

P O

Power Out

Regulator Output

P I/O

Power Out

Supply to a voltage domain and regulator Output

I /O

Digital Signal

Pad

All Digital Pads are I

/O Pads which are configured internally as required.

- All are configured as Push-Pull e

xcept those marked as OD (open drain)

- All have hysteresis by default, but is onl

y mentioned when it is required for correct

system operation.

A I

Analog Input

A O

Analog Output

AI/O

Analog Input/

Output

Bidirectional analog pad.

PU

Internal Pull Up

PD

Internal Pull

Down

s

t

n

e

m

m

o

C

n

o

i

t

p

i

r

c

s

e

D

e

p

y

T

d

a

P

SEMC Troubleshooting Manual

100

(115)

Summary of Contents for C702

Page 116: ...www s manuals com ...