C905

1222-9526 rev. 1

APPENDIX

A

P

P

E

NDIX

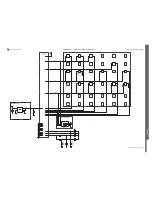

Components - N1300, N2206, N2212, N2213

Pinout Top View

A

B

C

D

E

F

G

H

J

K

L

M

N

FM_GND

FM_VA

FM_GPIO3

FM_GPIO2

FM_GPIO1

FM_VD

FM_GND

FM_LOUT

FM_GND

FM_GND

BT_RSRV_CL

FM_FMIP

BT_RSRV_N BT_RSRV_CL

FM_GND

FM_ROUT

FM_GND

BT_RSRV_DSM

FM_GND

FM_RFGND

FM_RSTB

BT_VSSANA

BT_HVA

NC

FM_GND

FM_VIO

BT_VSSANA

FM_RCLK

FM_SDIO

FM_SENB

BT_HVA

BT_VSSANA

BT_HVA

BT_VDD_CLD

BT_HVA

BT_CLK_

REQ_IN1

BT_HOST_WAKEUP

BT_SPI_INT

FM_SCLK

BT_VSSANA

BT_VSSANA

BT_VSSANA

BT_REF_CLK_IN

BT_VSSANA

NC

NC

BT_CLK_REQ_IN2

BT_TEST2

BT_VSSANA BT_VSSANA

BT_AF_PRG

BT_VSSANA

BT_UART_TXD

BT_SPI_DO

BT_VIO_E

BT_GPIO_0

BT_TEST1

BT_VSSANA

BT_VSSANA

BT_VSSDIG

BT_VSSRF

BT_VSSDIG

BT_VSSDIG BT_UART_RXD

BT_SPI_DI

BT_VSSRF

BT_GPIO_16 BT_REG_CTRL

BT_UART_RTS

BT_SPI_CSN

BT_RFN

BT_CLK_

REQ_OUT1

BT_CLK_

REQ_OUT2

BT_VIO_B

BT_VSSRF

BT_GPIO_11 BT_GPIO_10

BT_PCM_A BT_UART_CTS

BT_SPI_CLK

BT_RFP

BT_RESETN

BT_VSSDIG

BT_LP_CLK

BT_HVA

BT_GPIO_8

NC

NC

NC

BT_VSSRF

BT_CONFIG_1 BT_VSSDIG

BT_WAKEUP

BT_GPIO_9 BT_PCM_CLK BT_PCM_B

BT_VIO_A

BT_CONFIG_2

BT_RSRV_RF

BT_RSRV_D

BT_PCM_SYNC BT_VIO_D

BT_CONFIG_3

BT_HVD

BT_VIO_C

1

2

3

4

6

7

8

9

5

Pin Description and Assignment

The table shows the pin list of the STLC2593.

In columns “Reset” and “Default after reset”, the “PD/PU” shows the pads implementing an internal pull-

down/up for the internal Bluetooth section.

The column “Reset” shows the state of the pins during hardware reset; the column “Default after reset”

shows the state of the pins after the hardware reset state is left, but before any software parameter down-

load.

The column “Type” describes the pin directions:

– I for Input (All inputs have a Schmitt trigger function.)

– O for Output

– I/O for Input/Output

– O/t for tri-state output

For the output pin the default drive capability is 2 mA, except for pin K3 (BT_GPIO_11) and pin L3

(BT_GPIO_8) where it is 8 mA such that when used for Class 1, these 2 pins can be used for a switch

control in a cheaper way.

The STLC2593 Pin List (Functional and Supply)

Bluetooth Section

Name

Pin

#

Description

Type

Reset

(1)

Default

(2)

after reset

Clock and Reset Pins

BT_RESETN

K7 Global reset - active low

BT_REF_CLK_IN

F6

Reference clock input

(3)

I

Input

Input

BT_LP_CLK

K9 Low power clock input

SW Initiated Low Power mode

BT_CLK_REQ_OUT_1

J7

Wake-up signal to Host (Active high or Active

low, depending on configuration pins)

I/O

(4)

Input PD/PU,

depends on

config

Output

depends on

config

BT_CLK_REQ_OUT_2

J8

Wake-up signal to Host. Active low

s

d

n

e

p

e

d

O

/

I

U

P

t

u

p

n

I

)

y

l

n

o

e

d

o

m

I

P

S

(

on config

BT_CLK_REQ_IN_1

E7 Clock request input

D

P

t

u

p

n

I

D

P

t

u

p

n

I

)

h

g

i

h

e

v

it

c

A

(

BT_CLK_REQ_IN_2

F9 Clock request input

U

P

t

u

p

n

I

U

P

t

u

p

n

I

)

w

o

l

e

v

it

c

A

(

BT_HOST_WAKEUP/

BT_SPI_INT

E8 Wake-up signal to Host or SPI interrupt

Input PD

Output

BT_WAKEUP

L9

Wake-up signal to Bluetooth (Active high)

I/O

Input

(5)

Input

UART Interface

BT_UART_RXD/

BT_SPI_DI

H9

UART receive data

I/O

(4)

Input PD

Input PD

D

P

t

u

p

n

I

n

i

a

t

a

d

I

P

S

BT_UART_TXD/

BT_SPI_DO

G7

h

g

i

h

t

u

p

t

u

O

a

t

a

d

ti

m

s

n

a

r

t

T

R

A

U

D

P

t

u

p

n

I

t

u

o

a

t

a

d

I

P

S

BT_UART_CTS/

BT_SPI_CLK

K6

UART clear to send

Input PU

Input PU

D

P

t

u

p

n

I

k

c

o

l

c

I

P

S

BT_UART_RTS/

BT_SPI_CSN

J6

w

o

l

t

u

p

t

u

O

d

n

e

s

o

t

t

s

e

u

q

e

r

T

R

A

U

U

P

t

u

p

n

I

t

c

e

l

e

s

p

i

h

c

I

P

S

PCM Interface

BT_PCM_SYNC

N4 PCM frame signal

BT_PCM_CLK

M4 PCM clock signal

BT_PCM_A

K5 PCM data

BT_PCM_B

M5 PCM data

JTAG Interface

BT_GPIO_9

M3 JTAG_TDI or GPIO

BT_GPIO_11

K3 JTAG_TDO or GPIO

BT_GPIO_10

K4 JTAG_TMS or GPIO

BT_GPIO_16

J3

JTAG_NTRST (Active low) or Alternate

BT_GPIO_8

L3

JTAG_TCK or GPIO

General Purpose Input/Output Pins

BT_GPIO_0

G9 General purpose I/O

Configuration Pins

BT_CONFIG_1

L7

N

O

C

_

T

B

BT_CONFIG_3

N6

RF Signals

BT_RFP

K1

BT_RFN

J1

Power Supply

BT_HVA

BT_HVD

N7

BT_VIO_A

M6

BT_VIO_C

N3

BT_VIO_D

N5

BT_VIO_E

G8

BT_VIO_B

J9

BT_VDD_CLD

E6

Bluetooth Section

Name

I/O

(4)

Input PD

Input PD

Input PU

(6)

Input PU

(6)

Input PD

(6)

Input PD

(6)

I/O

(4)

Input PU

(6)

Input PU

(6)

function

Input PD

(6)

Input PD

(6)

Input PD

(6)

Input PD

(6)

I/O

(4)

Input PD

Input PD

t

u

p

n

I

t

u

p

n

I

I

l

a

n

g

i

s

n

o

it

a

r

u

g

if

n

o

C

7

M

2

_

G

I

F

Differential RF port

I/O

L2

Power supply (Connect to 2.75 V)

D3

E1

E2

E4

1.65 V to 2.85 V I/Os supply

(7)

1.17 V to 2.85 V I/Os supply

(7)

System clock supply

1.65 V to 2.85 V

(Connect to BT_VIO_A in case of a digital

reference clock input, to BT_VSSANA in case

of an analog reference clock input.)

Pin

#

Description

Type

Reset

(1)

Default

(2)

after reset

H6

H7

BT_VSSDIG

H8

Digital ground

K8

L8

D1

D2

E3

F1

F2

F3

BT_VSSANA

F4

Analog ground

G1

G3

G4

H3

H4

BT_VSSRF

H1

RF ground

L1

J2

RF regulator ground

K2

BT_TEST1

H2

O

/I

n

i

p

t

s

e

T

Input

(8)

Input

(8)

BT_TEST2

G2

BT_AF_PRG

G6 Test pin (Leave unconnected)

(9)

I/O

Open

Open

FM Radio Section

FM_GND

A3

FM ground (connect to ground plane on PCB)

B4

B6

B7

C4

C6

C7

D5

FM_VA

A4

Analog supply voltage (may be connected

directly to battery)

FM_VD

B3

Digital supply voltage (may be connected

directly to battery)

FM_GPIO1

A7

FM_GPIO2

A6 General purpose FM input/output

I/O

Input/Output

Input/Output

FM_GPIO3

A5

FM_FMIP

B8 FM RF input

FM_ROUT

C5 FM right audio output

FM_LOUT

B5 FM left audio output

FM_RFGND

C8

FM RF ground (connect to ground plane on

PCB)

Bluetooth Section

Name

Pin

#

Description

Type

Reset

(1)

Default

(2)

after reset

1.

Pin behaviour during HW reset (BT_RESETN low).

2.

Pin behaviour immediately after HW reset and internal chip initialization, but before SW parameter download.

3.

See also pin BT_VDD_CLD.

4.

Reconfigurable I/O pin.The functionality of these I/Os can be configured through software parameter download

5.

Should be strapped to BT_VSSDIG if not used.

6.

JTAG mode.

7.

Described in section 4.3.

8.

To be strapped to BT_VSSANA.

9.

Pin is ST - reserved for test function and it must be soldered to an isolated pad (not connected to anything, just floating).

10.

Described in section 5.8.

11.

Pin is not connected internally in the package; any connection can be done on board, in order to ease the board layout.

I

t

u

p

n

i

)

w

o

l

e

v

it

c

A

(

t

e

s

e

r

M

F

9

C

B

T

S

R

_

M

F

Input low

Input high

FM_VIO

D6 FM I/O supply voltage

FM_RCLK

D7 FM External reference oscillator input

I

Input

Input

FM_SDIO

D8 FM Serial data input / output

I/O

Input/Output

Input/Output

FM_SENB

D9 FM Serial enable input (active low)

I

Input

Input

t

u

p

n

I

t

u

p

n

I

I

t

u

p

n

i

k

c

o

l

c

l

a

ir

e

S

M

F

9

E

K

L

C

S

_

M

F

Other Pins

BT_RSRV_CL

B2

Test pin (Leave unconnected)

(9)

C3

BT_RSRV_D

M8

BT_RSRV_DSM

C1

BT_RSRV_N

C2

BT_RSRV_RF

M2

BT_REG_CTRL

J4

Regulator control pin

(10)

I/O

Input PD

Output high

NC

D4

Any use

(11)

F7

F8

L4

L5

L6

N1300 Bluetooth and RDS FM Radio Tuner 1200-9840

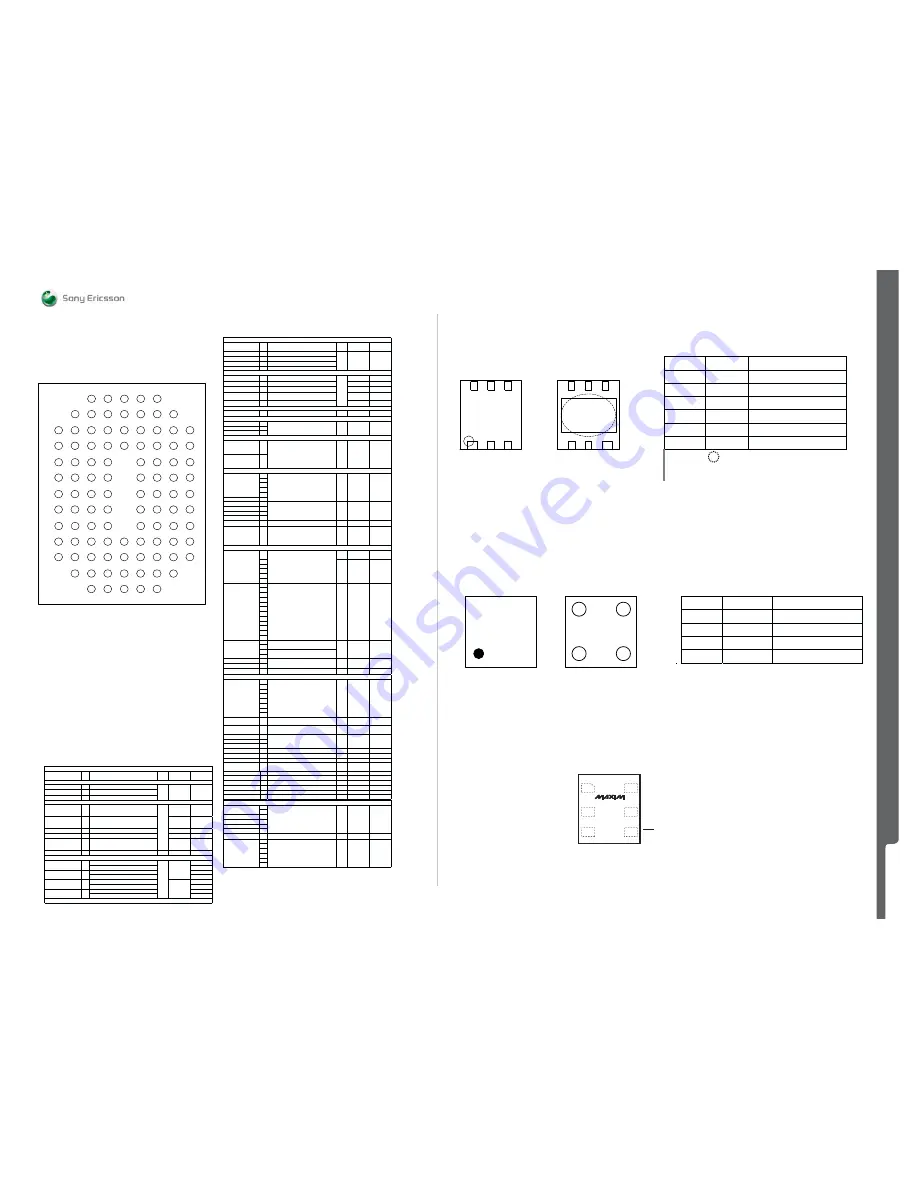

Top View

6

5

4

1

2

3

Bottom View

4

5

6

3

2

1

Pin No.

Symbol

Description

V

1

OUT2

Output Pin 2

V

2

DD

Input Pin

V

3

OUT1

Output Pin 1

GND

Ground Pin

1

n

i

P

e

l

b

a

n

E

p

i

h

C

1

E

C

5

CE2

Chip Enable Pin 2

* Tab in the parts have GND level.

(They are connected to the reverse side of this IC.)

Do not connect to other wires or land patterns.

6

4

PIN CONFIGURATION

Mark Side

Bump Side

4

1

3

2

4

1

3

2

PIN DESCRIPTIONS

Pin No.

Symbol

Description

1

V

DD

Input Pin

2

NC

No Connection

3

GND

Ground Pin

4

V

OUT

Output Pin

GND

OUT

1

+

IN

GND

LX

MAX8640Y

MAX8640Z

TOP VIEW

2

3

6

5

4

SHDN

μ

DFN

1.5mm x 1.0mm

Pin Configuration

N2206 LDO Dual 2.8V & 1.8V 1201-6517

N2212 LDO Regulator 150mA 1200-1974

NN2213 Step Down Converter 500mA 1208-4678

SEMC Troubleshooting Manual

105

(124)