C905

1222-9526 rev. 1

APPENDIX

A

P

P

E

NDIX

Components - N2500, N2700, N3100

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

Pin Name

Pin

Number

Pin Name

A1

GND

D5

I.C

H2

PLLVDD

L14

U70_SOUT

A2

GND

D6

SDRVDD

H3

I.C

M1

GND

A3

GND

D7

GND

H4

GND

M2

PM0_SI

A4

PO7

D8

GND

H5

GND

M3

I.C

A5

IOVDD

D9

SDRVDD

H10

GND

M4

PM1_SEN

A6

SPI0_SK

D10

I.C

H11

GND

M5

L1VDD

A7

SPI0_CSZ D11

L0VDD

H12

I.C

M6

YUV_VS

A8

SPI1_SK

D12

I.C

H13

GIO_P3

M7

YUV_DATA5

A9

SPI1_CSZ

D13

PO1

H14

GIO_P2

M8

YUV_DATA2

A10

IOVDD

D14

PO0

J1

GND

M9

SDRVDD

A11

INT_B

E1

IOVDD

J2

TCLKO

M10

L1VDD

A12

GND

E2

IOVDD

J3

I.C

M11

I.C

A13

GND

E3

L1VDD

J4

SDRVDD

M12

I.C

A14

GND

E4

I.C

J5

I.C

M13

I.C

B1

GND

E5

I.C

J10

I.C

M14

GND

B2

GND

E6

I.C

J11

SDRVDD

N1

GND

B3

L0_DET

E7

GND

J12

I.C

N2

GND

B4

PO6

E8

GND

J13

GIO_P1

N3

PM1_SI

B5

IOVDD

E9

I.C

J14

GIO_P0

N4

PM1_SO

B6

SPI0_SO

E10

I.C

K1

IOVDD

N5

IOVDD

B7

SPI0_SI

E11

L1VDD

K2

IOVDD

N6

YUV_HS

B8

SPI1_SO

E12

L1VDD

K3

L1VDD

N7

YUV_DATA6

B9

SPI1_SI

E13

IOVDD

K4

I.C

N8

YUV_DATA3

B10

IOVDD

E14

IOVDD

K5

I.C

N9

YUV_DATA0

B11

PLLMODE

F1

GND

K6

I.C

N10

IOVDD

B12

I.C

F2

GND

K7

GND

N11

PO2

B13

GND

F3

I.C

K8

GND

N12

I.C

B14

GND

F4

SDRVDD

K9

I.C

N13

GND

C1

GND

F5

I.C

K10

I.C

N14

GND

C2

RESETZ

F6

I.C

K11

L1VDD

P1

GND

C3

L1_DET

F10

I.C

K12

L1VDD

P2

GND

C4

I.C

F11

SDRVDD

K13

IOVDD

P3

GND

C5

L1VDD

F12

I.C

K14

IOVDD

P4

PM1_CLK

N2500 Companion Chip MP202 1200-4120

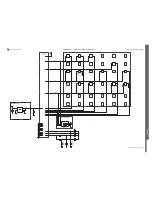

S1D13771 Pinout Diagram

S1D13771 W-CSP 64-pin Pinout Diagram (Top View)

Note

Pins marked as NC are not used and must be left unconnected. Pins marked as Reserved

must be left unconnected, unless otherwise specified.

S1D13771 W-CSP 64-pin Pinout (Top View)

1

2

3

4

5

6

7

8

A

NC

GPIO3

TE

COREVDD

D/C#

MD2

MD4

NC

A

B

TESTEN

VSS

GPIO_INT

CS#

IOVDD

VSS

MD5

SCANEN

B

C

Reserved

GPIO2

RESET#

VSS

WE#

IOVDD

MD6

MD7

C

D

VSS

GPIO1

IOVDD

CS#SEL

RD#

MD3

IOVDD

COREVDD D

E COREVDD

GPIO0

VSS

LCDCS#

MD0

Reserved COREVDD

VSS

E

F

DACVCC

DACVCC

DACVEE

VSS

MD1

VSS

PLLVSS

PLLVDD

F

G

DACVEE

DACVEE

VREF

IOVDD

COREVDD

IOVDD

VSS

VCP

G

H

NC

AOUT

VADJ

TEST0

TEST1

VSS

CLKI

NC

H

1

2

3

4

5

6

7

8

TOP VIEW

H

G

F

E

D

C

B

A

These marks are for reference only

and do not appear on the top of

the package.

8

7

6

5

4

3

2

1

PIN CONNECTIONS

A3

B3

C3

A2

B2

C2

A1

B1

C1

INM

OUTA

INP

VM_P

VM

V

p

BYPASS OUTB SHUTDOWN

9

−

Pin Flip

−

Chip CSP

(Top View)

PIN DESCRIPTION

Pin

Type

Symbol

Description

A1

I

INM

Negative input of the first amplifier, receives the audio input signal. Connected to the

feedback resistor R

f

and to the input resistor R

in

.

A2

O

OUTA

Negative output of the NCP2990. Connected to the load and to the feedback resistor Rf.

A3

I

INP

Positive input of the first amplifier, receives the common mode voltage.

B1

I

VM_P

Power Analog Ground.

B2

I

VM

Core Analog Ground.

B3

I

V

p

Positive analog supply of the cell. Range: 2.2 V

−

5.5 V.

C1

I

BYPASS

Bypass capacitor pin which provides the common mode voltage (Vp/2).

C2

O

OUTB

Positive output of the NCP2990. Connected to the load.

C3

I

SHUTDOWN

The device enters in shutdown mode when a low level is applied on this pin.

N3100 IC CS-9 1200-9978

N2700 TV Out Graphics Engine 1200-0362

SEMC Troubleshooting Manual

108

(124)