C905

1222-9526 rev. 1

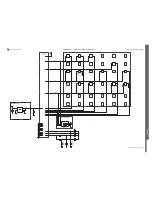

FUNCTIONAL OVERVIEW

Platform Block Diagram

FU

N

C

T

IO

N

A

L O

V

E

R

V

IE

W

FUNCTIONAL OVERVIEW

FU

N

C

T

IO

N

A

L O

V

E

R

V

IE

W

RF_DATA_B

RF_DATA_STRB

RF_DATA_A

RF_DATA_C

TXADC

PWRRST

MCLK

CLKREQ

IRQAcc

I2C BUS Internal Acc and App

Mobile SDRAM

xxx Mbit

CKE

CLK

CS

WE

CAS

RAS

BA1

BA0

UDQM

LDQM

D(0-15)

VDD

VDDQ

VSS

VSSQ

A13

A14

SDCKE

CLK

CS(0-2)

WE

OE/CAS

ADV/RAS

BE0

BE1

1.8 V

VIO

SRST

SCLK

I2S BUS

I2CSDA2

I2CSCL2

1.8 V

VIO

IRQApp

WTX_In

WTX_Ip

WTX_Qp

WTX_Qn

VIO

Backup

capacitor

2.65 V

VANA

1.2/1.05 V

VCORE

Backup

Cap

I

2

C

SLEEP

CONTROL

32 kHz

osc

SYSTEM

POR

100k

100k

100k

Power Management

AB 3100

PWRRST

XTAL_OUT

RF LDO a

EGG/WBTX

150 mA ;

2.8 V

Camera

LDOh

100 mA ;

2.75 V

MemCard

LDOg

100 mA ;

2.85 V

IR LDOk

200 mA

2.75 V

Analog

LDOf

30 mA

2.5~1.05V

I/O/Core

LDOe

200 mA

1.8~0.9V

Level

shift

G

LDO LP

2.2 V

OTP

64 bits

1MHz

OSC

PLL

44/48

IRQa

FUEL

GAUGE

ADDER

VIBRATOR

CONTROL

LED Control

ADC

10bit

AUTO

CTL

M

U

X

I2C

I2C

LDO d

200 mA ;

2.65 V

VDDLP

Internal BUCK

1.8 to 0.9 V

5%

600 mA

BOOST

(Soft start)

6-22 V, 30 mA

BAND

GAP

IRQb

2.5 V

VANA

2.8 V

VRAD

2.75 V

VCAM+Display

2.85 V

VCARD

2.75 V

VIR

VBAT

VBAT

VBAT

VBAT

32KHZ

VBAT

VBAT

VBAT

On/Off

Switch

LDOc

200 mA

2.65 V

VBACKUP

VANA

2.65 V

VANA

2.5 V

VANA

1.8 V

VIO

1.2/1.05 V

VCORE

1.2/1.05 V

VCORE

1.8 V

VIO

1.8 V

VIO

1.8 V

VIO

1.2/1.05 V

VCORE

1.8 V

VIO

1.2/1.05 V

VCORE

VRTC

VBAT

2.75 V

LED interface

Vibrator if

WLED interface

SIM interface

Memory interface

WTXPOW_DET

WRX0_In

WRX0_Ip

WRX0_Qp

WRX0_Qn

100

mohm

25

mohm

IMEAS

VMEAS

S-D

ADC

CHREG

CHSENSE-

FGSENSE-

DCIO

VBUS

UART

BDATA

I2C

TRICKLE

VBAT

DCIO

DCIO

DET

USB

DET

USB CHRG

CONTROL

DCIO CHRG

CONTROL

SIM

LDO

GND

CLK

RST

DAT

NC

SIM card

VCC

C1

C2

C3

C5

C6

C7

SERCON

DACO0

DACO1

DACO2

DACO3

DAC3

11 bits

DAC0

11 bits

DAC1

11 bits

DAC2

11 bits

RF_CTRL_CLK

RF_CTRL_DATA

RF_CTRL_STRB0

RF_CTRL_STRB1

WRFCTRL3

WDAC2

WDAC1

ANTSW2

ANTSW0

ANTSW1

ANTSW3

CIVSYN

CIHSYN

CIRES

CIPCLK

R0

R1

R2

R3

R4

R5

C0 C1 C2 C3 C4

1

8

7

6

5

4

3

2

0

9

#

C

Y

N

*

1.8 V

VIO

S

L

2.85 V

VCARD

1.8 V

VIO

Bluetooth

Radio

PCMCLK

PCMSYN

PCMDLD

PCMULD

RESOUT2

SYSCLKREQ1

VBAT

REG

2.75V

1.8 V

VIO

RESETOUT0

EMIF2_ALE_A18

EMIF2_CLE_A17

EMIF2_WE

EMIF2_SDCAS_RE_OE

EMIF2 CS0

SDCKE

SDCLK

SDCS

WE

SDCAS

SDRAS

BE0

BE1

A14

A15

ATMS

Microphone

GPA4

I2CSDA2

I2CSCL2

I2CSDA2

I2CSCL2

USB if

BT SPI CLK

BT SPI CS

BT SPI DI

BT SPI DO

1.8 V

VIO

Debug Interface

ACB/

Debug

Debug

equipm.

VIO

1.8 V

GPIOif

C

O

N

D+

D-

GND

VBUS

uP

SAFETY

VBAT

BDATA

BATTERY

GND

LED Control

VBAT_C

VDD_REF

1uF

DCIO_INT

32KHz

SYSCLK1

32KHz

SYSCLK1

1.8 V

VIO

External to Platform

Internal to Platform

V_TEMP

TEMP_BIAS

Placed

close to RF

TEMP_BIAS

LCDTEMP

Placed

close to

LCD

Digital

Baseband

Controller

Decaps

VBAT

VIO 1.8V

HS_DIR

HS_STP

HS_CLOCK

HS_NXT

HS_DAT0-7

HS-USB Transceiver with ULPI, ISP 1508

ULPI

if logic

Serializer

Deserializer

CLOCK

D0-D7

DIR

STP

NXT

Reg

map

USB 2.0 ATX

Termination

Resistors

POR

PLL

DP

DM

OSC

XI

XO

1

ID det

ID

VBUS

Comp

Chrg/

dischrg

resistors

VBUS

Voltage

regulators

VBAT

VDD1V8

VDD3V3

Internal

power

PSW_N

Int Ref

Voltage

REF

VIO

SYSCLK2n

ULPI_CS

CSn

To NAND WP

EMIF2 NFIF READY

DB 3210 POP

NAND Flash 1 Gbit

DB 3210 POP

SDRAM 512 Mbit

VBAT

2.75 V

VRAD

VBAT

VccWPA

Power

coupler

RF Pow det

Det

En

UL: 1920 – 1980 MHz

DL: 2110 – 2170 MHz

UL: 1850 – 1910 MHz

DL: 1930 – 1990 MHz

UL: 824 – 849 MHz

DL: 869 – 894 MHz

824 – 915 MHz

1710 – 1910 MHz

1930 – 1990 MHz

1805 – 1880 MHz

925 – 960 MHz

869 – 894 MHz

WDCDCREF

RFCtrl1

Switch

PWM/PFM

En

Control

Logic

RF_CTRL_CLK

RF_CTRL_DATA

RF_CTRL_STRB0

2.8 V

VRAD

1.8 V

VIO

RF_DATA_STRB

RF_DATA_B

RF_DATA_C

RF_DATA_A

LNA

LNA

LNA

LNA

LNA

A

D

A

D

0

90

LPF

+

ChP

PhD

÷

N.M

VCO

LPF

ChP

PhD

÷

N.M

+

0

90

+

DAC

DAC

XO

DAC

VCO

VCO

LNA

LNA

WCDMA LB

WCDMA HB1

WCDMA HB2

WCDMA HB3

CLK

DATA

STROBE

Serial

Control

WTxQB

WTxQA

WTxIB

WTxIA

GSM/EDGE

AM

DAC

RFCtrl1

RFCtrl2

RFCtrl1

RFCtrl2

GSM/

EDGE HB

GSM/

EDGE LB

WCDMA LB

WCDMA HB

WCDMA HB

GSM/EDGE

LB

GSM/EDGE

LB

GSM/EDGE

HB

GSM/EDGE

HB

WRxIA

WRxIB

WRxQB

WRxQA

EDataB

EDataA

EDataC

EDataStr

RF 3300 WCDMA/GSM/GPRS/EDGE TRX

MCLKsec

CLKREQ

MCLK

XO

XOp

26MHz X-tal

TestOut

RF_CTRL_CLK

RF_CTRL_DATA

RF_CTRL_STRB1

1.8 V

VIO

LNA

LNA

LNA

LNA

LNA

A

D

A

D

0

90

LPF

+

ChP

PhD

÷

N.M

VCO

LPF

ChP

PhD

÷

N.M

+

0

90

+

DAC

DAC

XO

DAC

VCO

VCO

LNA

LNA

WCDMA LB

WCDMA HB1

WCDMA HB2

WCDMA HB3

CLK

DATA

STROBE

Serial

Control

WTxQB

WTxQA

WTxIB

WTxIA

GSM/EDGE

AM

DAC

RFCtrl1

RFCtrl2

RFCtrl1

RFCtrl2

GSM/

EDGE HB

GSM/

EDGE LB

WCDMA LB

WCDMA HB

WCDMA HB

GSM/EDGE

LB

GSM/EDGE

LB

GSM/EDGE

HB

GSM/EDGE

HB

WRxIA

WRxIB

WRxQB

WRxQA

EDataB

EDataA

EDataC

EDataStr

RF 3300 WCDMA RX (other functions unused)

MCLKsec

CLKREQ

MCLK

XO

XOp

TestOut

GSM/EDGE

PA + Ant Sw.

VAPC

PA

PA

GSM850/

900 Input

DCS/PCS

Input

ESD

VccWPA

En

Bias

VccWPA

En

Bias

VccWPA

En

Bias

WRX1_In

WRX1_Ip

WRX1_Qp

WRX1_Qn

WRFCTRL0

WRFCTRL1

WRFCTRL2

RX Diversity for WCDMA

I2S_CLK0

I2S_WS0

I2S_RX0

I2S_TX0

I2S_CLK1

I2S_WS1

I2S_RX1

I2S_TX1

PCM

DECODER

ENCODER

ADC

2

ADC

1

DAC

1

DAC

2

SIDE

TONE

TX

PGA2

TX

PGA1

RX

PGA1

RX

PGA2

CCO

Audio Part AB 3100

PCMO

PCMI

PCMSYN

PCMCLK

CCO1

ADC

3

TX

PGA3

DAC

3

RX

PGA2

CCO2

Vol

Vol

Vol

PCMO

PCMI

PCMSYN

PCMCLK

LINE1

LINE2

MIC1P

PGA

VSSBEAR

VDDBEAR

VSS_SPKR

VDD_SPKR

MIC2N

MIC3N

MIC4N

VMID

PCM/

I2S

Inter-

face 2

PCM/

I2S

Inter-

face 1

DAC

4

RX

PGA2

Vol

PGA

PGA

PGA

VDDDIG

ADC2REF

ADC3REF

MS PRO

IO Bridge

26 MHz

DSP

Sub System

PDROM

464kB

SRAM

332 kB

CRU

GPIO

Timer0

XpertCEVA

JTAG

Timer1

AHB Slave

8

ANT_SW1

RF_DATA_STRB

RF_DATAA0

RF_DATAC2

RF_DATAB1

IRAM

7k x 32

bit

32

32

52 MHz

AHB IF

SYS

CON

GPIO

Watch

Dog

Cable

Detect

Event

Hist

Bus

Tracer

EMIF1

AHB Slave

EMIF Control

AHB Slave

EMIF Arbiter

CTS/RTS

ANT_SW0

SIMIF

SIM_RSTn

SIM_CLK

AHB

Default

slave

AHB

IF

DMA

58 Channels

50 Requests

AHB

IF

AHB

IF

RESOUT0n

RESOUT1n

PWRRSTn

RESOUT2n

RTCCLKIN

MSACCIRQn

APPSLEEP

MSAPPIRQn

SYSCLK0REQ

SYSCLK0

MCLK

MCLKREQ

ACCSLEEP

ARM9 Sub system

ARM926

D

Cache

32 kB

I

Cache

32 kB

AHB

Master

MMU

I Mem

Control

D Mem

Control

ARM9EJ-S

TLB

AHB BUS IF

AHB

Master

EMIF2

AHB Slave

Shared EMIF

EMIF

I2C1

MMC/SD

AHB2APB

26 MHz

I2S/

PCM0

AHB

Slave

I2S/

PCM1

I2C2

DMA

40 Channels

40 Requests

AHB

Slave

AHB

Master

APEX

AHB

Slave

APEX

RAM

APEX

ROM

APEX+

AHB

Slave

AHB

Master

Video

Enc

RAM0

Video

Encoder

AAIF

AHB IF

MSL

AAIF

AHB IF

MSL

UART 0

SPI

RX/TX

CTS/RTS

CS0 -2

DI/DO/CLK

ARB

AHB

Slave

DMA

AHB IF

AHB2APB

26 MHz

SERVICEn

DPLL

APLL

ARB

AHB Master

Random noise

generator

SDA

SCL

ANT_SW2

ADC

SYSCLK2

SYSCLK1

APLL

IO

IO

IO

Core

DAC_Q_POS

DAC_Q_NEG

DAC_I_POS

DAC_I_NEG

TX_POW

WINT-

COM

WSYS-

CON

WTIM-

GEN

52 MHz

WCDMA SUB System

IM

Bridge

AHB

Slave +

Sequ.

EGG

Sub System

RFWB ENABLE 0

RFWB ENABLE 1

RFWB ENABLE 3

RF CTRL CLK

RF CTRL DATA

TIM

GEN

SER

CON

CLK

CON

VA

DFSE

GSM

CRYPTO

16

32+5

32+3

32+3

32+3

32+3

16

26 MHz

16

16

32+5

16

16

TXIF

RXIF

RFIF

32+5

32+3

32+3

32+5

16

16

16

TX ADC STRB

26 MHz

ARM9 Sub system

ARM926

D

Cache

32 kB

I

Cache

32 kB

AHB

Master

MMU

I Mem

Control

D Mem

Control

ARM9EJ-S

TLB

DTCM

8 kB

ITCM

26 kB

ETM IF

ETM9

AHB BUS IF

JTAG DEBUG

TCM IF

EICE

AHB

Master

To Mux

TXRX

RF CTRL STRB1

RF CTRL STRB0

INTCON

EDC

ETX

Access

Timer

Boot ROM

8k x 32 bit

ARB

ARB

ARB

ANT_SW3

O

R

NAND Flash IF

ECC

AHB Slave

I2CSCL2

I2CSDA2

MC_CMD/BS

MC_CMDDIR

MC_DATADIR

MC_CLK

CDI

PDI

PAR/ SSI

AHB

Slave

GRAM

64k byte

GAMCON

AHB

Master

MCiDCT

(Video)

PDICON

CDICON

GAMEACC

(3D)

XGAM

KEYPAD

GPIO

INTCON

32

TIMER0

16

32

2

16

WDOG

32

SYSCON

16

AHB2APB

13 MHz

AHB

Slave

RTC

16

BUS TR

32

Event H

32

DPLL

208M

APLL

13M

32kHz

DCON

RF CTRL STRB2

GSM PA ENABLE

RFWB ENABLE 4

RFWB ENABLE 5

Digital Baseband

Controller DB 3210

H

15

ADC1_Q_POS

ADC1_Q_NEG

ADC1_I_POS

ADC1_I_NEG

ADC2_Q_POS

ADC2_Q_NEG

ADC2_I_POS

ADC2_I_NEG

CEVA-

X1622

DRAM

128 kB

IRAM

64 kB

ICU

PMU

Video

Enc

RAM1

AHB2AHB

52 MHz

Boot

ROM

MS

PRO

32

32

UART 0

PPM

32

32

KEYOUT(0-4)

TIMER1

32

FS_USB/

HS_USB

WCDMA

Integrity

I2C0

SPI

UART2

RS232

IRDA

BT

UART3

I

2

S/PCM

(BT)

UART0

GPRS

CRYPTO

AHB2APB

26 MHz

WCDMA

Cipher 0,1

All 48 GPIOs here

have switchable

pullups.

VBAT

20

21

22

23

26

27

25

24

28-35

Data Card

MS Pro

MMC/SD

Resistors

2.65 V

VAUDIO

2.65 V

VAUDIO

VBAT

MCLK

CLKREQ

MClkSec

MClkSec

WRFCTRL3

WTXPOW_DET

VBAT

EX1030 Filters

CCO

CCO

Hook

PHF

Jack

Band V

Band II

Band I

To Camera

2.75 V

VCAM

1.8 V

VIO

SYSCLK0

LDO

2.8 V

2.8 V

VRAD

2.8 V

VRAD2

VBAT

2.8 V

VRAD2

Camera 1

Camera 2

CIPCLK

CIVSYN

CIHSYN

CIRES

I2CSDA2

I2CSCL2

MMC CLK

CAM 2 STBY

CAM 1 STBY

CAM POW

CAM POW

CAM 1 STBY

CAM 2 STBY

Image

proc

A

D

C

Sensor

Control

CKE

CLK

CS

WE

CAS

RAS

UDQM

LDQM

D(0-15)

VDD

VDDQ

VSS

VSSQ

BA0

BA1

WP

CE

RE

WE

CLE

ALE

D(0-7)

VDD

VSS

R/B

GPA4

GPA4

MCLK SEC

BT + WLAN

Power

coupler

Power

coupler

Band 1

Band 2

Band 5

2.75 V

VCAM

VBAT

S U B - L C D

VBAT

L C D

1.8 V

VIO

32kHz

SPI

WLAN

INT

VIO

1.8V

VBAT

Power Down

MCLK SEC

SYSCLKREQ1

VIO

1.8V

VBAT

VIR

2.75V

VIO

1.8V

Vcc

RXD

I/O &

Supply

Log &

Contr

MODE

TXD

RC

COM

P

IRDA

AMP

IRDA_RX

IRDA_TX

IRDA_SD

Bluetooth

Baseband

BT SPI IRQ

SEMC Troubleshooting Manual

99

(124)