6-3

BKP-5090

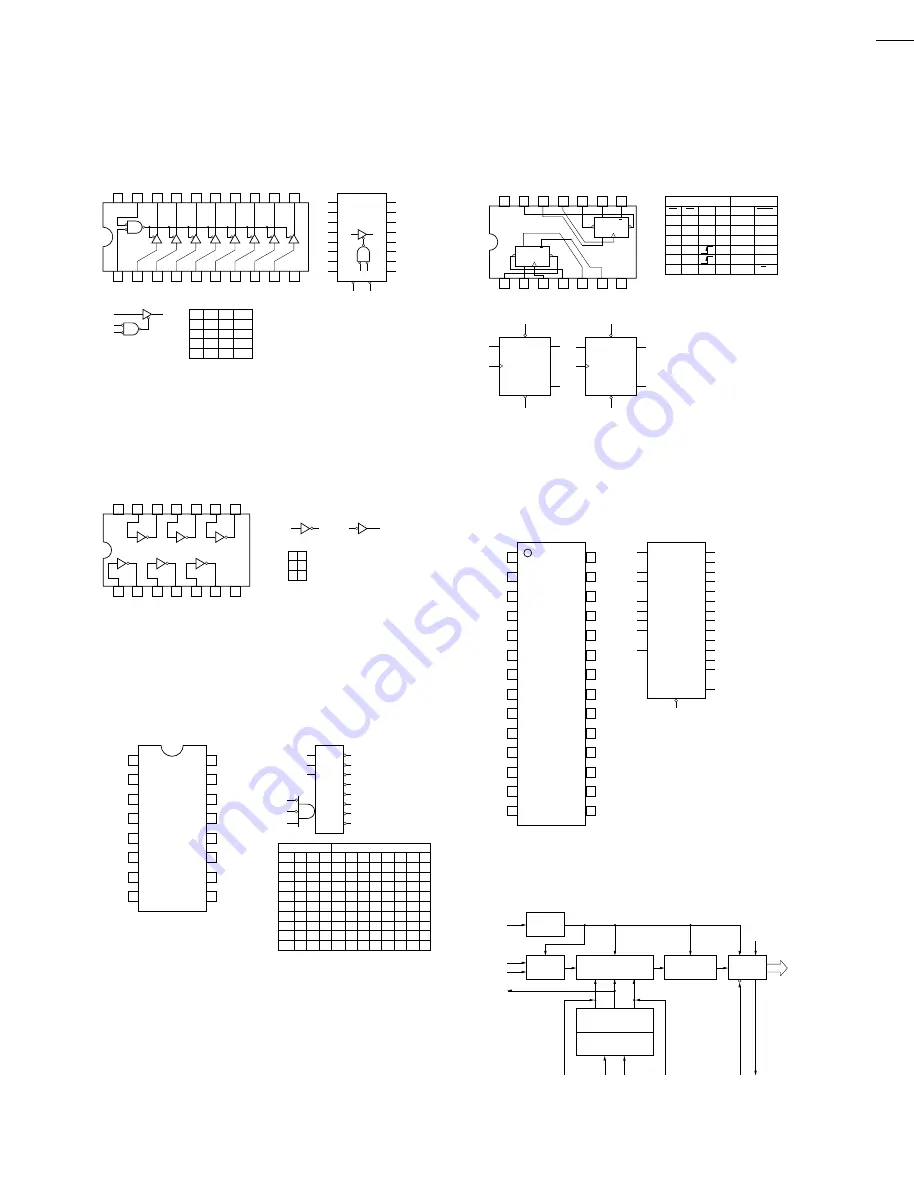

IC

74LCX541MTCX (NS)

74VHC74MTCX (NS)FLAT PACKAGE

TC74VHC74FT(EL) (TOSHIBA)FLAT PACKAGE

G1

G2

0

0

x

1

A

0

1

x

x

G1

0

0

1

x

Y

0

1

HI-Z

HI-Z

0

1

x

HI-Z

V

DD

Y5

Y2

G2

Y1

Y4

A5

A4

A2

A1

G1

GND

8

13

16

15

14

7

6

5

1

2

3

4

17

18

20

19

9

10

12

11

A3

Y3

Y8

Y7

Y6

A7

A6

A8

Y

A

G1

G2

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

G2

1

19

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

: HIGH IMPEDANCE

A1

A2

A3

A4

A5

A6

A7

A8

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

C-MOS BUFFERS AND LINE DRIVERS WITH 3-STATE OUTPUTS

—TOP VIEW—

74VHC04MTCX (NS)FLAT PACKAGE

SN74HCT04APW-E05 (TI)FLAT PACKAGE

A

A

Y =

Y

14

13

V

DD

GND

12

11

10

9

8

7

6

5

4

3

2

1

A

0

1

Y

1

0

0 : LOW LEVEL

1 : HIGH LEVEL

Y =

A

C-MOS HEX INVERTERS

—TOP VIEW—

74VHC138MTCX (NS)FLAT PACKAGE

TC74VHC138FT(EL) (TOSHIBA)FLAT PACKAGE

EN

0

1

1

1

1

1

1

1

1

Y7

1

1

1

1

1

1

1

1

0

Y6

1

1

1

1

1

1

1

0

1

Y5

1

1

1

1

1

1

0

1

1

Y4

1

1

1

1

1

0

1

1

1

Y3

1

1

1

1

0

1

1

1

1

Y2

1

1

1

0

1

1

1

1

1

Y1

1

1

0

1

1

1

1

1

1

Y0

1

0

1

1

1

1

1

1

1

C

x

0

0

0

0

1

1

1

1

B

x

0

0

1

1

0

0

1

1

A

x

0

1

0

1

0

1

0

1

V

DD

IN

IN

IN

IN

IN

IN

OUT

INPUTS

OUTPUTS

1

2

3

4

5

6

7

A

B

C

EN1

EN2

EN3

Y7

8

10

11

12

13

14

15

16

9

0

1

x

EN =

EN1

•

EN2

• EN3

GND

OUT

4

1

2

3

15

14

13

A

B

C

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

EN

5

6

EN1

EN2

EN3

Y0

OUT

Y1

OUT

Y2

OUT

Y3

OUT

Y4

OUT

Y5

OUT

Y6

12

11

10

9

7

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

C-MOS 3-TO-8 LINE DECODER/DEMULTIPLEXER

—TOP VIEW—

S

D

0

1

0

1

1

1

R

D

1

0

0

1

1

1

CK

x

x

x

0

D

x

x

x

1

0

x

Qn

+

1

1

0

1

1

0

Qn

Qn

+

1

0

1

1

0

1

Qn

INPUTS

OUTPUTS

0

1

x

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

2

3

5

1

6

12

11

9

13

4

10

8

R

D

R

D

D

D

Q

Q

Q

Q

S

D

S

D

R

D

S

D

Q

D

Q

R

D

S

D

Q

D

Q

14

13

V

DD

GND

12

11

10

9

8

7

6

5

4

3

2

1

C-MOS DUAL D-TYPE FLIP-FLOPS WITH DIRECT SET/RESET

—TOP VIEW—

ADS805E-T2 (BURR-BROWN)FLAT PACKAGE

C-MOS 12-BIT A/D CONVERTER

—TOP VIEW—

28

25

23

22

19

18

20

14

VDRV

ANA

+

ANA

_

REFT

VREF

SEL

REFB

CLK

OVR

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

CM

1

2

3

4

5

6

7

8

9

10

11

12

13

21

OVR

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

CLK

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

V

DD

GND

GND

GND

V

DD

15

OE

: ANALOG (

+

)

: COMPLEMENTARY ANALOG

: CONVERT CLOCK

: OUTPUT ENABLE

: BOTTOM REFERENCE VOLTAGE

: TOP REFERENCE VOLTAGE

: INPUT RANGE SELECT

: OUTPUT DRIVER VOLTAGE

: REFERENCE VOLTAGE SELECT

: COMMON MODE VOLTAGE

: DATA BIT

: OVER RANGE INDICATOR

VDRV

ANA

+

ANA

_

REFT

CM

REFB

VREF

SEL

OE

INPUT

ANA

+

ANA

_

CLK

OE

REFB

REFT

SEL

VDRV

VREF

OUTPUT

CM

D0 - D11

OVR

TIMING

CIRCUIT

CLK

14

T/H

ANA

+

25

12-BIT

PIPELINED

A/D CONVERTER

ERROR

CORRECTION

LOGIC

3-STATE

OUTPUTS

ANA

_

23

REFERENCE LADDER

AND DRIVER

REFERENCE AND

MODE SELECT

CM

21

REFT

22

VREF

19

SEL

18

REFB

20

OE

15

OVR

1

D0 - D11

2 - 13

VDRV

28