2-27

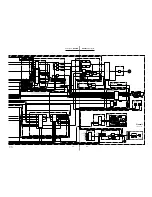

BVP-900

BVP-900P

IC

1

2

3

4

8

7

6

5

GND

V

DD

(

+

2 to

+

6 V)

1

2

A

B

7 Y

5

6

3

A

0

0

1

1

B

0

1

0

1

Y

1

1

1

0

0 ; LOW LEVEL

1 : HIGH LEVEL

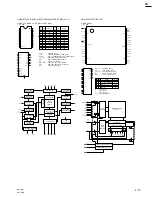

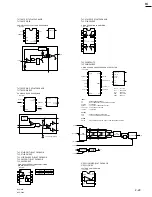

C-MOS DUAL 2-INPUT NAND GATE

—TOP VIEW—

A

B

Y

Y = A • B = A + B

C-MOS 2-INPUT EXCLUSIVE OR GATE

(SCALE 6/1)

—TOP VIEW—

1

2

GND 3

5 V

DD

4

A

B

2

1

4

Y

A

0

0

1

1

B

0

1

0

1

TYPE

7S86FU

7S86F

4S30F

7SH86FU

V

DD

+

2 to

+

6V

Y

0

1

1

0

0 ; LOW LEVEL

1 ; HIGH LEVEL

Y = A • B

+

A • B

+

3 to

+

18V

+

2 to

+

5.5V

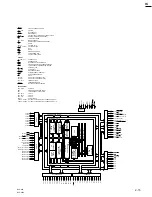

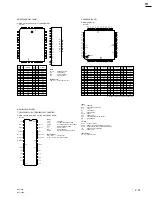

TC74VHC163F (TOSHIBA)FLAT PACKAGE

TC74VHC163FS(EL)

TC74VHC163FT(EL) (TOSHIBA)FLAT PACKAGE

TC74VHCT138AFT(EL) (TOSHIBA)

TC74VHCT138FS(EL) (TOSHIBA)

TC7S08FU(TE85R) (TOSHIBA)FLAT PACKAGE

TC7S32FU(TE85R) (TOSHIBA)FLAT PACKAGE

TC7SH32FU-TE85R (TOSHIBA)FLAT PACKAGE

TC7ST32FU(TE85R) (TOSHIBA)FLAT PACKAGE

TC7S66FU (TOSHIBA)

TC7S66FU(TE85R)

TC7S86FU (TOSHIBA)CHIP PACKAGE

TC7S86FU(TE85R)

TC7W00FU (TOSHIBA)CHIP PACKAGE

TC7W00FU(TE12R)

—TOP VIEW—

1

2

GND 3

5 V

DD

4

A

B

A

B

Y =

2

1

4

Y

A

0

0

1

1

B

0

1

0

1

TYPE

7S32F

7S32FU

4S71F

7SH32FU

7ST32FU

V

DD

+

2 to

+

6 V

Y

0

1

1

1

0 : LOW LEVEL

1 : HIGH LEVEL

Y = A

+

B = A • B

+

3 to

+

18 V

+

2 to

+

5.5 V

+

5 V

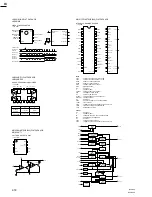

C-MOS 2-INPUT OR GATE

C-MOS ANALOG SWITCH

(

+

12V MAX)

V

DD

GND

CONT

OUT/IN

IN/OUT

5

4

1

2

3

—TOP VIEW—

(SCALE 6/1)

1

2

GND 3

5 V

DD

4

A

B

A

B

Y =

2

1

4

Y

A

0

0

1

1

B

0

1

0

1

TYPE

7S08F

7S08FU

4S81F

14S81F

7SH08FU

7SH08F

V

DD

+

2 to

+

6V

Y

0

0

0

1

0 ; LOW LEVEL

1 ; HIGH LEVEL

Y = A • B = A

+

B

+

3 to

+

18V

+

2 to

+

5.5V

C-MOS 2-INPUT AND GATE

—TOP VIEW—

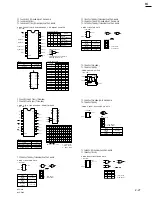

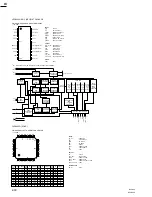

C-MOS 3-TO-8 LINE DECODER / DEMULTIPLEXER

EN

0

1

1

1

1

1

1

1

1

Y7

1

1

1

1

1

1

1

1

0

Y6

1

1

1

1

1

1

1

0

1

Y5

1

1

1

1

1

1

0

1

1

Y4

1

1

1

1

1

0

1

1

1

Y3

1

1

1

1

0

1

1

1

1

Y2

1

1

1

0

1

1

1

1

1

Y1

1

1

0

1

1

1

1

1

1

Y0

1

0

1

1

1

1

1

1

1

C

X

0

0

0

0

1

1

1

1

B

X

0

0

1

1

0

0

1

1

A

X

0

1

0

1

0

1

0

1

V

DD

IN

IN

IN

IN

IN

IN

OUT

INPUTS

OUTPUTS

1

2

3

4

5

6

7

A

B

C

EN1

EN2

EN3

Y7

8

10

11

12

13

14

15

16

9

0 ; LOW LEVEL

1 ; HIGH LEVEL

X

; DON'T CARE

EN = EN1 • EN2 • EN3

GND

OUT

4

1

2

3

15

14

13

A

B

C

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

EN

5

6

EN1

EN2

EN3

Y0

OUT

Y1

OUT

Y2

OUT

Y3

OUT

Y4

OUT

Y5

OUT

Y6

12

11

10

9

7

TYPE

74HCT

74ACT/74HCT/74VHCT

74AC/74VHC

OTHER TYPES

NOTE:

V

DD

+

5 V

+

4.5 to

+

5.5 V

+

2 to

+

5.5 V

+

2 to

+

6 V

—TOP VIEW—

C-MOS PRESETTABLE SYNCHRONOUS 4-BIT BINARY COUNTER

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

QD

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

QC

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

QB

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

QA

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

V

DD

IN

IN

IN

IN

IN

IN

IN

COUNT

OUTPUTS

1

2

3

4

5

6

7

RD

CK

A(DATA A)

B(DATA B)

C(DATA C)

D(DATA D)

EN1

8

10

11

12

13

14

15

16

9

COUNT SEQUENCE

CARRY OUTPUT "CO"

CO IS HIGH WHEN EN2 INPUT IS

HIGH AND COUNT IS "15".

GND

OUT

3

4

5

11

14

13

A

B

C

6

D

2

7

10

QA

LD

RD

9

QB

QC

QD

CO

EN1

EN2

EN2

QD

QC

QB

QA

CO

CO

OUT

QA

OUT

QB

OUT

QC

OUT

QD

IN

EN2

IN

LD

1

12

15

TYPE

HC

AC/VHC

HCT/ACT/FCT

NOTE:

V

DD

+

2 to

+

6V

+

5V

+

2 to

+

5.5V

RD

0

1

RESET

(SYNCHRONOUS)

PRESET

(SYNCHRONOUS)

NO COUNT

NO COUNT

COUNT

LD

X

0

EN1

X

X

EN2

X

X

1

1

0

X

1

1

X

0

1

1

1

1

MODE

MODE SELECTION

CONTROL INPUTS

—TOP VIEW—

Summary of Contents for BVP-900 Series

Page 4: ......

Page 30: ......

Page 36: ......

Page 160: ......

Page 167: ......

Page 181: ......

Page 193: ......

Page 224: ......

Page 272: ......

Page 275: ......

Page 278: ......

Page 282: ......

Page 363: ......

Page 384: ......

Page 396: ......

Page 404: ......

Page 408: ......

Page 411: ......

Page 412: ......

Page 414: ......

Page 454: ......

Page 455: ......

Page 479: ......

Page 480: ......

Page 482: ......

Page 498: ......

Page 519: ......

Page 520: ......