2-11

BVP-900

BVP-900P

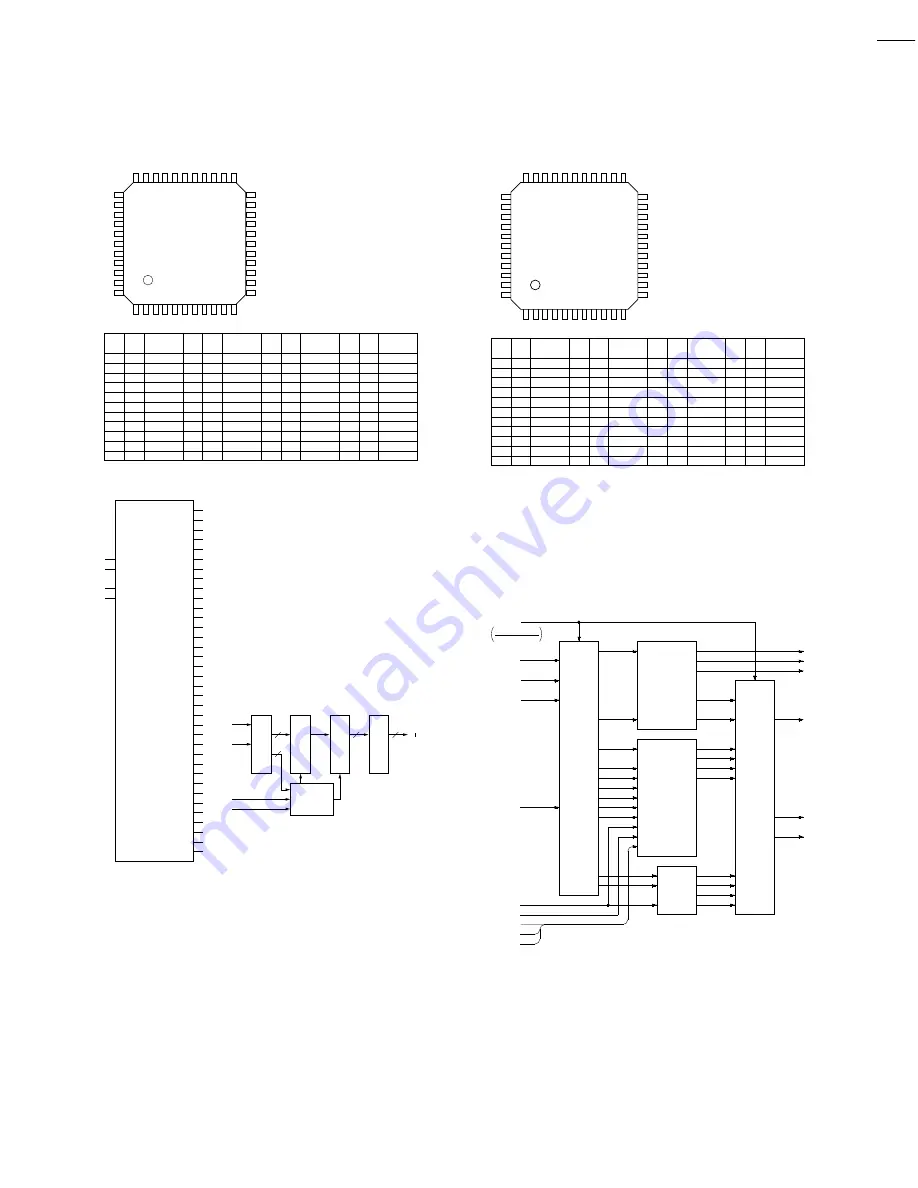

IC

C-MOS PULSE GENERATOR

—TOP VIEW—

1

2

3

4

5

6

7

8

9

10

11

22

21

20

19

18

17

16

15

14

13

12

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

V

DD(

+

5.0V)

GND

PIN

No.

I/O

SIGNAL

SIGNAL

I/O

No.

PIN

SIGNAL

I/O

No.

PIN

SIGNAL

I/O

No.

PIN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

—

I

I

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

—

O

I

O

O

O

I01

I02

I03

I04

I05

I06

I07

I08

MODE

I09

I10

I11

I12

I13

I14

I15

GND

A19

I17

RST

CKH

TES2

TEST

OT00

OT01

OT02

OT03

OT04

OT05

OT06

OT07

OT08

OT09

OT10

OT11

OT12

OT13

OT14

OT15

CLK

OT16

RAM

ROM

V

DD

(V

DD

=

+

5.0V)

I01 - I17

RST

OT00 - OT16

; I NPUT

; RESET

; OUTPUT

MODE

; MODE SELECT

(H : WINDOW GEN / L : CHIP SELECT LOGIC)

A19

; ADDRESS INPUT

CKH

INPUT

; FOR TEST

CLK

; CLOCK

TES2

; FOR TEST

TEST

; FOR TEST

OUTPUT

RAM

; RAM OUT

ROM

; ROM OUT

1

2

3

4

5

6

7

8

9

10

11

GND

33

32

31

30

29

28

27

26

25

24

23

V

DD

(

+

4.5V to

+

5.5V)

12

13

14

15

16

17

18

19

20

21

22

GND

44

43

42

41

40

39

38

37

36

35

34

V

DD

(

+

4.5V to

+

5.5V

)

PIN

NO.

1

2

3

4

5

6

7

8

9

10

11

I/O

I

O

O

O

O

—

O

O

O

O

O

SYMBOL

MODE

O00

O01

O02

O03

GND

O04

O05

O06

O07

O08

PIN

NO.

12

13

14

15

16

17

18

19

20

21

22

I/O

O

O

O

O

O

—

O

O

O

O

O

SYMBOL

O09

O10

O11

O12

O13

GND

O14

O15

O16

O17

O18

PIN

NO.

23

24

25

26

27

28

29

30

31

32

33

I/O

O

O

O

O

O

—

O

O

O

O

O

SYMBOL

O19

O20

O21

O22

O23

V

DD

O24

O25

O26

O27

O28

PIN

NO.

34

35

36

37

38

39

40

41

42

43

44

I/O

O

O

O

O

O

—

O

O

I

I

I

SYMBOL

O29

O30

O31

O32

O33

V

DD

O34

O35

SEDA

LD

SOCK

(V

DD

=

+

4.5V to

+

5.5V)

—TOP VIEW—

C-MOS SERIAL TO PARALLEL CONVERTER

CXD8072Q (SONY)FLAT PACKAGE

CXD8344AQ (SONY)

2

3

4

5

7

8

9

10

11

12

13

14

15

16

18

19

20

21

22

23

24

25

26

27

29

30

31

32

33

34

35

36

37

38

40

41

O00

O01

O02

O03

O04

O05

O06

O07

O08

O09

O10

O11

O12

O13

O14

O15

O16

O17

O18

O19

O20

O21

O22

O23

O24

O25

O26

O27

O28

O29

O30

O31

O32

O33

O34

O35

42

44

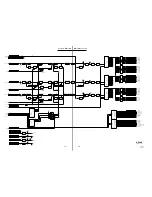

1

43

SEDA

SOCK

MODE

LD

LD

MODE

SEDA

SOCK

O01-O35

; LOAD PULSE

; MODE SELECT

; SERIAL DATA

; SERIAL CLOCK

; OUTPUT

SHIFT

REGISTER

LATCH

SELECTOR

BUFFER

MODE

DETECTOR

& LATCH

CONTROL

12

SEDA

44

SOCK

43

LD

1

MODE

4

12

36

36

O00

O35

2 - 5, 7 - 16

18 - 27,29 - 38, 40, 41

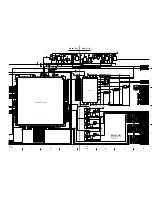

9

MODE

WINDOW /

1 - 8

I01 - I08

I09 - I15

10 - 16

A4 - A19

CHIP

SELECT

LOGIC

INPUT

SELECTOR

AS

RAM

43

RAM

ROM

44

ROM

24 - 32

OT00 - OT08

IO9 - IO15

EE PROM

OUTPUT

SELECTOR

WINDOW

GEN

DT0 - DT7

MAD

WRB

CSB

HD

VD

N/P

GM O

SU WO

AI WO

TESG

19

I17

fH GEN &

CLOCK

BUFFER

FH

M9

M18

M18B

CLK

41

RST

20

CKH

21

TES2

22

TEST

23

33 - 38

OT09 - OT14

OT15

40

OT16

42

CHIP SELECT

FH M1

FH M2

/

3

/

8

/

8

/

16

/

7

/

9

/

6

/

7

18

A19

(at MODE "L")

(at MODE "H")

IO0 - IO8

Summary of Contents for BVP-900 Series

Page 4: ......

Page 30: ......

Page 36: ......

Page 160: ......

Page 167: ......

Page 181: ......

Page 193: ......

Page 224: ......

Page 272: ......

Page 275: ......

Page 278: ......

Page 282: ......

Page 363: ......

Page 384: ......

Page 396: ......

Page 404: ......

Page 408: ......

Page 411: ......

Page 412: ......

Page 414: ......

Page 454: ......

Page 455: ......

Page 479: ......

Page 480: ......

Page 482: ......

Page 498: ......

Page 519: ......

Page 520: ......