2-46

BVW-55

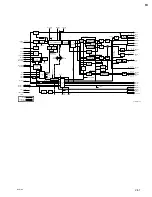

IC

CXD8818R (SONY)

GND V

DD

H

GND V

DD

L

GND

GND

GND V

DD

L

181

185

190

195

200

205

210

215

220

225

230

235

240

C-MOS MEMORY CONTROLLER

—TOP VIEW—

120

115

110

105

100

95

90

85

80

75

70

65

61

180

175

170

165

160

155

150

145

140

135

130

125

121

1

5

10

15

20

25

30

35

40

45

50

55

60

V

DD

L

GND

V

DD

H

GND

GND

V

DD

L

GND

V

DD

H

GND

GND

V

DD

H

GND

V

DD

L

GND

GND

V

DD

H

GND

V

DD

L

V

DD

L

GND

V

DD

H

GND

GND

V

DD

L

GND

V

DD

H

GND

PIN

NO.

I/O

I/O

I/O

PIN

PIN

NO.

NO.

SIGNAL

SIGNAL

SIGNAL

I/O

PIN

NO.

SIGNAL

PIN

NO.

I/O

SIGNAL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

V

DD

L

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

144

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

210

211

212

213

214

215

216

217

218

219

220

221

209

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

I

I

I

I

I

—

—

I

I

I

I

I

I

I

I

I

O

—

—

I

I

I

I

I

I

I

I

I

I

—

I

I

I

I

I

I

I

I

I

I

I

—

—

I

I

I

I

I

I

I

I

I

I

—

—

I

I

I

O

O

I

O

I

O

O

—

—

I

O

O

O

I

I

I

I

I

—

—

I

I

I

I

I

I

O

O

O

O

O

—

O

I

I

I

I

I

I

I

I

I

—

—

I

I

O

I

I

I

I

I

I

I

I

—

—

I

I

I

I

I

O

O

O

O

O

—

—

O

O

O

O

O

O

O

O

O

O

—

—

O

O

O

O

O

O

O

O

O

O

—

O

O

O

O

I

I

I

I

I

I

O

—

—

I

I

I

I

I

I

I

I

I

I

—

—

I

I

I

I

I

I

O

I

I

I

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

—

—

I

I

I

O

O

O

O

I

I

O

O

—

O

O

O

O

O

O

O

O

O

O

—

—

O

O

O

O

I

I

I

I

I

I

—

I

I

I

I

I

M2CF

M3D9

M3D8

M3D7

M3D6

GND

M3D5

M3D4

M3D3

M3D2

M3D1

M3D0

M3HD

M3VD

M3CF

SAVP

V

DD

H

GND

DED9

DED8

DED7

DED6

DED5

DED4

DED3

DED2

DED1

DED0

GND

DECCK

DEHD

DEVD

DECF

DEP

DICPST

DICR

DICF2

DICF1

DICF0

V

DD

L

GND

DID9

DID8

DID7

DID6

DID5

DID4

DID3

DID2

DID1

DID0

V

DD

H

GND

DIHD

DIVD

DIP

CHD

CVD

ISY

HR

SFTHR

SMPP

PCEN

V

DD

L

GND

W27

DTHP

CH

CLPP

A1D9

A1D8

A1D7

A1D6

A1D5

V

DD

H

GND

A1D4

A1D3

A1D2

A1D1

A1D0

A1P

YCER

BCER

RCER

COE

HFCK

GND

QTCK

A2D9

A2D8

A2D7

A2D6

A2D5

A2D4

A2D3

A2D2

A2D1

V

DD

L

GND

A2D0

A2P

IVST

M1D9

M1D8

M1D7

M1D6

M1D5

M1D4

M1D3

M1D2

V

DD

H

GND

M1D1

M1D0

M1HD

M1VD

M1CF

ICF0

ICF1

ICF2

MWY9

MWY8

V

DD

L

GND

MWY7

MWY6

MWY5

MWY4

MWY3

MWY2

MWY1

MWY0

MWP

MWFIN

V

DD

H

GND

MWC9

MWC8

MWC7

MWC6

MWC5

MWC4

MWC3

MWC2

MWC1

MWC0

GND

MWCK

RDY9

RDY8

RDY7

RDY6

RDY5

RDY4

WRSTL

V

DD

L

GND

RDY3

RDY2

RDY1

RDY0

RDP

RDFIN

RDC9

RDC8

RDC7

RDC6

V

DD

H

GND

RDC5

RDC4

RDC3

RDC2

RDC1

RDC0

RDRSTL

ASTB

V

DD

L

GND

MAD7

MAD6

MAD5

MAD4

MAD3

MAD2

MAD1

MAD0

MPUCK

V

DD

H

GND

R27

ADVCF

TEST

SRP

REFCF0

REFCF1

REFCF2

FNTC

R18

SUPT

GND

BD9

BD8

BD7

BD6

BD5

BD4

BD3

BD2

BD1

BD0

V

DD

L

GND

BHD

BVD

BCF

BP

M2D9

M2D8

M2D7

M2D6

M2D5

M2D4

M2D3

I

—

V

DD

H

GND

M2D2

M2D1

M2D0

M2HD

M2VD

58

59

DIFCK

187

WR

RD

MWRST

MRCK

MRRST

RST

A1D0 - 9

A1P

A2D0 - 9

A2P

ADVCF

ASTB

DECF

DED0 - 9

DEHD

DEP

DEVD

DICF0 - 2

DICPST

DICR

DID0 - 9

DIFCK

DIHD

DIP

DIVD

FNTC

ISY

M1CF

M1D0 - 9

M1HD

M1VD

M2CF

M2D0 - 9

M2HD

M2VD

M3CF

M3D0 - 9

M3HD

M3VD

R27

RD

RDC0 - 9

RDFIN

RDP

RDY0 - 9

RST

SFTHR

TEST

W27

WR

INPUT

; A/D CONVERTED Y SIGNAL DATA PARITY

; ADVANCED REFERENCE COLOR FRAME

; MPU INTERFACE ADDRESS STROBE

DECK

; DIF (SERIAL DIGITAL) INPUT CF

; DIF (SERIAL DIGITAL) INPUT DATA

; DIF (SERIAL DIGITAL) INPUT CLOCK

; DIF (SERIAL DIGITAL) INPUT HD

; DIF (SERIAL DIGITAL) INPUT PARITY

; DIF (SERIAL DIGITAL) INPUT VD

; FORCED NTSC MODE

; ANALOG COMPONENT SYNC INPUT

; MULTI-LOOP (1) INPUT CF FOR SELF-DIAG.

; MULTI-LOOP (1) INPUT HD FOR SELF-DIAG.

; MULTI-LOOP (1) INPUT VD FOR SELF-DIAG.

; MULTI-LOOP (2) INPUT CF

; MULTI-LOOP (2) INPUT DATA

; MULTI-LOOP (2) INPUT HD

; MULTI-LOOP (2) INPUT VD

; MULTI-LOOP (3) INPUT COLOR FRAME FOR SELF-DIAG.

; MULTI-LOOP (3) INPUT DATA FOR SELF-DIAG.

; MULTI-LOOP (3) INPUT HD FOR SELF-DIAG.

; MULTI-LOOP (3) INPUT VD FOR SELF-DIAG.

; MEMORY READ Y DATA

; MEMORY READ R-Y/B-Y DATA

; MEMORY READ DATA FINISH BLOCK ID BIT

; MEMORY READ DATA PARITY

; MASTER RESET

; SHIFTED HR INPUT

; TEST MODE ENABLE

; 27MHz CLOCK LOCKED TO ANALOG COMPONENT

; MPU INTERFACE WRITE REQUEST

; REFERENCE 27MHz CLOCK

; MPU INTERFACE READ REQUEST

; A/D CONVERTED Y SIGNAL DATA FROM DIGITAL FILTER

; A/D CONVERTED R-Y/B-Y SIGNAL DATA FROM DIGITAL FILTER

; A/D CONVERTED R-Y/B-Y SIGNAL DATA PARITY

; DIF (SERIAL DIGITAL) INPUT COMPOSITE FLAG (H : COMPOSITE)

; DIF (SERIAL DIGITAL) INPUT CRCC ERROR FLAG (H : ERROR)

; MULTI-LOOP (1) INPUT DATA FOR SELF-DIAG.

; COMPOSITE DECODER INPUT CLOCK

; COMPOSITE DECODER INPUT CF

; COMPOSITE DECODER INPUT DATA

; COMPOSITE DECODER INPUT HD

; COMPOSITE DECODER INPUT PARITY

; COMPOSITE DECODER INPUT VD

OUTPUT

BCER

BCF

BD0 - 9

BHD

BP

BVD

CH

CHD

CLPP

COE

CVD

DTHP

HFCK

HR

ICF0 - 2

IVST

MPUCK

MRCK

MRRST

MWC0 - 9

MWCK

MWFIN

MWP

MWRST

MWY0 - 9

PCEN

QTCK

R18

RCER

RDRSTL

REFCF0 - 2

SAVP

SMPP

SRP

SUPT

WRSTL

YCER

INPUT/OUTPUT

MAD0 - 7

; B-Y SIGNAL CLAMP ERROR

; BUFFERED DATA

; COUNT H TIMING PULSE FOR PLL

; ANALOG COMPONENT ODD/EVEN OUTPUT

; CLAMP PULSE FOR ANALOG COMPONENT

; DITHER TIMING PULSE FOR A/D DITHER

; PHASE COMPARATOR PULSE OUT FOR PLL

; SELECTED INPUT SIGNAL COLOR FRAME

; MPU INTERFACE CLOCK (9MHz)

; MEMORY WRITE RESET PULSE

; MEMORY WRITE Y DATA OUTPUT

; PHASE COMPARATE ENABLE

; R-Y SIGNAL CLAMP ERROR

; MEMORY READ RESET LINE

; REFERENCE CF

; SAMPLING PULSE FOR PLL

; SERVO REFERENCE PULSE

; TIMING PULSE FOR SET-UP REMOVER

; MEMORY WRITE RESET LINE

; MPU INTERFACE DATA BUS

; BUFFERED CF

; BUFFERED HD

; BUFFERED PARITY

; BUFFERED VD

; ANALOG COMPONENT HD OUTPUT

; ANALOG COMPONENT VD OUTPUT

; SELECTED INPUT SIGNAL V-START PULSE

; MEMORY READ CLOCK

; MEMORY READ RESET PULSE

; MEMORY R-Y/B-Y DATA OUTPUT

; MEMORY WRITE CLOCK

; MEMORY WRITE DATA PARITY OUTPUT

; Y SIGNAL CLAMP ERROR

; 13.5MHz CLOCK (W27/2) FOR DIGITAL FILTER

; MEMORY WRITE DATA FINISH BLOCK ID BIT

; 18MHz CLOCK OUTPUT FOR PLAYER SELF-DIAG.

; 6.75MHz CLOCK (W27/4) FOR DIGITAL FILTER

; SELECTED INPUT SIGNAL SAV TIMING PULSE

Summary of Contents for BVW-55

Page 4: ......

Page 8: ......

Page 50: ...1 40 BVW 55 1 2 3 4 5 6 7 8 9 d l s d l 1 15 Fixtures and Adjustment Equipment List ...

Page 58: ......

Page 106: ......

Page 116: ......

Page 130: ......

Page 148: ......

Page 154: ......

Page 158: ......

Page 169: ...1 9 BVW 55 P2 1 2 Fixtures and Adjustment Equipment List 1 2 3 4 5 6 7 8 9 d l s d l ...

Page 176: ......

Page 272: ......

Page 384: ......

Page 392: ......

Page 396: ...1 2 BVW 55 ...

Page 666: ......

Page 705: ......

Page 752: ......

Page 780: ......

Page 805: ......

Page 848: ......

Page 856: ......

Page 870: ......

Page 884: ......

Page 904: ......

Page 909: ...5 27 b BVW 55 5 27 b CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 12 MB 838 MB 838 ...

Page 911: ...5 27 a BVW 55 5 27 a CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 11 MB 838 MB 838 ...

Page 940: ......