2-50

BVW-55

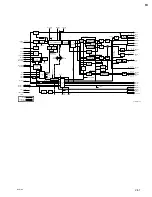

IC

CXD8821Q (SONY)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

GND

NC

NC

NC

GND

GND

GND

GND

GND

V

DD

V

DD

GND

V

DD

GND

GND

V

DD

V

DD

V

DD

NC

NC

NC

NC

NC

NC

NC

NC

NC

V

DD

V

DD

V

DD

V

DD

GND

GND

NC

NC

V

DD

GND

C-MOS AUDIO TIMING GENERATOR

—TOP VIEW—

V

DD

PIN

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

—

—

—

—

—

O

O

O

O

O

O

O

O

O

—

—

I

I

—

—

I

I

—

I

I

GND

V

DD

NC

V

DD

NC

FA2

FA1

FA0

PC2

PC1

PC0

LOCK

FREF

FCOMP

V

DD

GND

FSCK

FPCK

NC

NC

ACS

INCF

NC

T3

T2

I/O

SIGNAL

PIN

No.

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

I

—

—

—

—

—

O

O

O

O

O

O

O

—

—

—

—

O

O

O

O

O

O

O

—

T1

V

DD

NC

V

DD

GND

GND

DE0

DE7

DE8

FP0

FP5

FP6

FP7

NC

V

DD

GND

NC

FP8

FS0

FS5

FS6

FS7

FS8

FS9

GND

GND

V

DD

NC

V

DD

CRN

CFPI

SA0

SA1

SA2

SA3

SCK

STB

SI

SO

GND

V

DD

TO

NC

NC

NC

HD0

VD0

FOE1

HD1

VD1

I/O

SIGNAL

PIN

No.

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

—

—

—

—

I

I

I

I

I

I

I

I

I

O

—

—

O

—

—

—

O

O

O

O

O

I/O

SIGNAL

PIN

No.

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

O

—

—

—

—

—

O

O

O

O

O

O

—

—

I

—

—

O

O

O

O

O

O

O

—

DCK2

V

DD

NC

V

DD

GND

GND

HD2

VD2

CF2

HD3

VD3

CF3

NC

GND

CLK

GND

V

DD

DCK4

HD4

VD4

CF4

HD5

VD5

CF5

GND

I/O

SIGNAL

62

61

63

64

57

58

59

60

55

90

56

22

21

18

26

25

24

9

10

11

67

17

STB

SCK

SI

SO

SA0

SA1

SA2

SA3

CRN

CLK

CFPI

INCF

ACS

FPCK

T1

T2

T3

PC2

PC1

PC0

TO

FSCK

74

75

73

76

82

83

84

85

86

87

93

94

95

96

97

98

99

71

72

6

7

8

32

33

34

35

36

37

38

43

44

45

46

47

48

49

14

13

12

HD1

VD1

FOE1

DCK2

HD2

VD2

CF2

HD3

VD3

CF3

DCK4

HD4

VD4

CF4

HD5

VD5

CF5

HD0

VD0

FA2

FA1

FA0

DE0

DE7

DE8

FP0

FP5

FP6

FP7

FP8

FS0

FS5

FS6

FS7

FS8

FS9

FCOMP

FREF

LOCK

INPUT

ACS

CFPI

CLK

CRN

FPCK

FSCK

INCF

SA0 – 3

SCK

SI

STB

T1 – T3

OUTPUT

CF2

CF3

CF4

CF5

DCK2

DCK4

DE0 – 8

FA0 – 2

FCOMP

FOE1

FP0 – 8

FREF

FS0 – 9

HD0

HD1

HD2

HD3

HD4

HD5

LOCK

PC0 – 2

SO

TO

VD0

VD1

VD2

VD3

VD4

VD5

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

H: 48 kHz AUDIO L: 44.1 kHz AUDIO

INPUT CF PULSE

CLOCK

POWER ON RESET

AUDIO CLOCK (256FS) FOR PROGRAM PLAY

AUDIO CLOCK (512FS)

CF SIGNAL FOR VD2 REFORMING

SERIAL PRESET ADDRESS

SERIAL CLOCK

SERIAL INPUT DATA

SERIAL START PULSE

TEST PIN FOR IC

CF INFORMATION PULSE OF THE #2 GROUP (PROGRAMABLE)

CF INFORMATION PULSE OF THE #3 GROUP (PROGRAMABLE)

CF INFORMATION PULSE OF THE #4 GROUP (PROGRAMABLE)

CF INFORMATION PULSE OF THE #5 GROUP (PROGRAMABLE)

13.5 MHz CLOCK OF THE #2 GROUP (PROGRAMABLE)

13.5 MHz CLOCK OF THE #4 GROUP (PROGRAMABLE)

AUDIO CLOCK FOR PITCH CONTROL

AUDIO 5-FIELD SEQ. ID

AUDIO CLOCK FOR PLL

ODD/EVEN SIGNAL OF THE #1 GROUP (PROGRAMABLE)

AUDIO CLOCK FOR PROGRAM PLAY

REFERENCE CLOCK FOR AUDIO PLL

AUDIO CLOCK (FS9 : 512FS)

HD PULSE (UNPROGRAMABLE)

HD PULSE OF THE #1 GROUP (PROGRAMABLE)

HD PULSE OF THE #2 GROUP (PROGRAMABLE)

HD PULSE OF THE #3 GROUP (PROGRAMABLE)

HD PULSE OF THE #4 GROUP (PROGRAMABLE)

HD PULSE OF THE #5 GROUP (PROGRAMABLE)

AUDIO PLL LOCK DET

TEST PIN FOR IC

SERIAL OUTPUT DATA

TEST PIN FOR IC

VD PULSE (UNPROGRAMABLE)

VD PULSE OF THE #1 GROUP (PROGRAMABLE)

VD PULSE OF THE #2 GROUP (PROGRAMABLE)

VD PULSE OF THE #3 GROUP (PROGRAMABLE)

VD PULSE OF THE #4 GROUP (PROGRAMABLE)

VD PULSE OF THE #5 GROUP (PROGRAMABLE)

SERIAL

INTERFACE

DECODER

HD5,

VD5,

CF5,

GEN.

HD4,

VD4,

CF4,

GEN.

HD3,

VD3,

CF3,

GEN.

HD2,

VD2,

CF2,

GEN.

HD. VD. CF

GENERATOR

HD1,

VD1,

O/E,

GEN.

AUDIO CLOCK GENERATOR

74

75

73

76

82

83

84

85

86

87

93

94

95

96

97

98

99

HD1

VD1

FOE1

DCK2

HD2

VD2

CF2

HD3

VD3

CF3

DCK4

HD4

VD4

CF4

HD5

VD5

CF5

HD1 DLY

VD1 DLY

HD2 DLY

VD2 DLY

HD3 DLY

VD3 DLY

SA0 – SA3

CRN

STB

SCK

SI

SO

HD4 DLY

VD4 DLY

HD5 DLY

VD5 DLY

11

10

2

11

10

2

11

10

2

4

11

10

2

11

10

2

3

3

3

3

5

6

CF

HD

VD

71

72

6 – 8

32 – 34

35 – 38

44 – 49

9 – 11

67

HD0

VD0

FA2 – FA0

DE0, DE7, DE8

FP0, FP5 – FP8

FS0, FS5 – FS9

57 – 60

62

61

63

64

55

90

56

22

CLK

CFPI

INCF

21

18

ACS

FPCK

17

14

13

12

FSCK

26 – 24

T1 – T3

FCOMP

FREF

LOCK

PC2 – PC0

TO

(RESET)

Summary of Contents for BVW-55

Page 4: ......

Page 8: ......

Page 50: ...1 40 BVW 55 1 2 3 4 5 6 7 8 9 d l s d l 1 15 Fixtures and Adjustment Equipment List ...

Page 58: ......

Page 106: ......

Page 116: ......

Page 130: ......

Page 148: ......

Page 154: ......

Page 158: ......

Page 169: ...1 9 BVW 55 P2 1 2 Fixtures and Adjustment Equipment List 1 2 3 4 5 6 7 8 9 d l s d l ...

Page 176: ......

Page 272: ......

Page 384: ......

Page 392: ......

Page 396: ...1 2 BVW 55 ...

Page 666: ......

Page 705: ......

Page 752: ......

Page 780: ......

Page 805: ......

Page 848: ......

Page 856: ......

Page 870: ......

Page 884: ......

Page 904: ......

Page 909: ...5 27 b BVW 55 5 27 b CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 12 MB 838 MB 838 ...

Page 911: ...5 27 a BVW 55 5 27 a CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 11 MB 838 MB 838 ...

Page 940: ......