2-54

BVW-55

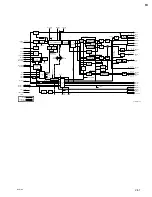

IC

CXD9001AR (SONY)

GND

V

DD

V

DD

GND V

DD

133

135

140

145

150

155

160

165

170

175

176

C-MOS CPU R3041 PERIPHERAL

—TOP VIEW—

88

85

80

75

70

65

60

55

50

45

132

130

125

120

115

110

105

100

95

90 89

1

5

10

15

20

25

30

35

40

44

V

DD

GND

GND

GND

GND

GND

GND

GND

NC

V

DD

V

DD

PIN

NO.

I/O

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

—

O

O

I

I

O

I

I

O

I

I

O

O

O

I

I

I

I

I

I

I

—

—

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

—

SIGNAL

V

DD

RDENN

WRENN

CTC1CLK0

CTC1G0

CTC1OUT0

CTC1CLK1

CTC1G1

CTC1OUT1

CTC1CLK2

CTC1G2

CTC1OUT2

EXTDENN

IOENN

BEN0

BEN1

BEN2

BEN3

A0

A1

A23

V

DD

GND

A24

A25

A26

A27

A28

D0

D1

D2

D3

D4

D5

D6

D7

FLASHCSN

SRAM1CS

SRAM2CS

WRENNA

WRENNB

WRENNC

WRENND

V

DD

PIN

NO.

I/O

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

—

—

I

I

O

I

O

I

I

O

I

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

SIGNAL

GND

GND

RESETN

SIOCLK

SIO1TXD

SIO1RXD

SIO1INT

SIO2CTS

SIO2DSR

SIO2TXD

SIO2RXD

SIO2INT

SIORDN

SIOWRN

SIOCDN

SIOBAN

PIO1P00

PIO1P01

PIO1P02

PIO1P03

PIO1P04

PIO1P05

PIO1P06

PIO1P07

TEST0

PIO1P10

PIO1P11

PIO1P12

PIO1P13

PIO1P14

PIO1P15

PIO1P16

PIO1P17

TEST1

PIO1P20

PIO1P21

PIO1P22

PIO1P23

PIO1P24

PIO1P25

PIO1P26

PIO1P27

GND

GND

PIN

NO.

I/O

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

O

O

I

I

O

I

I

O

I

I

O

O

O

I

—

SIGNAL

V

DD

PIO2P00

PIO2P01

PIO2P02

PIO2P03

PIO2P04

PIO2P05

PIO2P06

PIO2P07

TEST2

PIO2P10

PIO2P11

PIO2P12

PIO2P13

PIO2P14

PIO2P15

PIO2P16

PIO2P17

TEST3

PIO2P20

PIO2P21

V

DD

GND

PIO2P22

PIO2P23

PIO2P24

PIO2P25

PIO2P26

PIO2P27

S16W2CSN

S16W3CSN

CTC2CLK0

CTC2G0

CTC2OUT0

CTC2CLK1

CTC2G1

CTC2OUT1

CTC2CLK2

CTC2G2

CTC2OUT2

HALFCLK

V8W6CSN

VARWAITN

V

DD

PIN

NO.

I/O

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

—

—

I

I

I

I

I

I

I

I

O

I/O

I

O

O

O

I

I

I

I

I

I

O

O

—

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

—

—

SIGNAL

GND

GND

INTP0

INTP1

INTP2

INTP3

INTP4

INTP5

INTP6

INTP7

INT

SIO2BRK

EXTFRAME

FRAME

VINT

S8W4CSN

SYSCLKN

DATAENN

BURSTN

LASTN

RDN

WRN

ACKN

RDCENN

NC

S8W3CSN1

S8W3CSN2

S8W3CSN3

S8W3CSN4

S8W3CSN5

S8W3CSN6

V8W3CSN

FIFOREN1

FIFOREN2

FIFOREN3

FIFOREN4

FIFOWEN1

FIFOWEN2

FIFOWEN3

FIFOWEN4

FIFORCKN

IOENN2

GND

GND

INPUT

A0, A1

A23 - A28

BEN0

-

BEN3

BURSTN

CTC1CLK0 - CTC1CLK2

CTC1G0 - CTC1G2

CTC2CLK0 - CTC2CLK2

CTC2G0 - CTC2G2

DATAENN

EXTFRAME

INTP0 - INTP7

LASTN

RDN

RESETN

SIO1RXD

SIO2CTS

SIO2DSR

SIO2RXD

SIOCLK

SYSCLKN

TEST0 - TEST3

VARWAITN

WRN

OUTPUT

ACKN

CTC1OUT0 - CTC1OUT2

CTC2OUT0 - CTC2OUT2

EXTDENN

FIFORCKN

FIFOREN1 - FIFOREN4

FIFOWEN1 - FIFOWEN4

FLASHCSN

FRAME

HALFCLK

INT

IOENN

IOENN2

RDCENN

RDENN

S16W2CSN

S16W3CSN

S8W3CSN1 - S8W3CSN6

S8W4CSN

SIO1INT

SIO1TXD

SIO2INT

SIO2TXD

SIOBAN

SIOCDN

SIORDN

SIOWRN

SRAM1CS

SRAM2CS

V8W3CSN

V8W6CSN

VINT

WRENN

WRENNA - WRENND

INPUT/OUTPUT

D0 - D7

PIO1P00 - PIO1P07

PIO1P10 - PIO1P17

PIO1P20 - PIO1P27

PIO2P00 - PIO2P07

PIO2P10 - PIO2P17

PIO2P20 - PIO2P27

SIO2BRK

; ADDRESS BUS

; ADDRESS BUS

; 1st TO 4th BYTE SELECT

; CPU BURST

; CTC CLOCK

; CTC GATE

; CTC2 CLOCK

; CTC2 GATE

; CPU DATA ENABLE

; EXTERNAL FRAME

; INTERRUPT

; CPU LAST

; CPU READ

; CPU RESET

; SIO1 RECEIVE DATA

; SIO2 CTS

; SIO2 DSR

; SIO2 RECEIVE DATA

; SIO CLOCK

; CPU SYSTEM CLOCK

; TEST

; VARIABLE WAIT

; CPU WRITE

; CPU ACKNOWLEDGE

; CTC1 OUT

; CTC2 OUT

; READ/WRITE SELECT

; FIFO READ CLOCK

; FIFO READ ENABLE

; FIFO WRITE ENABLE

; FLASH ROM CHIP SELECT

; FRAME

; DIVIDED-BY-TWO SYSTEM CLOCK

; INTERRUPT

; DATA BUS DRIVER ENABLE

; 2nd DATA BUS DRIVER ENABLE

; CPU READ CHIP ENABLE

; READ

; 16-BIT 2-WAIT CHIP ENABLE

; 16-BIT 3-WAIT CHIP ENABLE

; 8-BIT 3-WAIT CHIP ENABLE

; 8-BIT 4-WAIT CHIP ENABLE

; SIO1 INTERRUPT

; SIO1 TRANSMIT DATA

; SIO2 INTERRUPT

; SIO2 TRANSMIT DATA

; SIO B/A

; SIO C/D

; SIO READ

; SIO WRITE

; SRAM1 CHIP SELECT

; SRAM2 CHIP SELECT

; VARIABLE WAIT 8-BIT 3-WAIT CHIP ENABLE

; VARIABLE WAIT 8-BIT 6-WAIT CHIP ENABLE

; FRAME INTERRUPT

; WRITE

; SRAM 1st TO 4th BYTE WRITE

; DATA BUS

; PIO1 PORT0

; PIO1 PORT1

; PIO1 PORT2

; PIO2 PORT0

; PIO2 PORT1

; PIO2 PORT2

; SIO2 SYNC/BRK

Summary of Contents for BVW-55

Page 4: ......

Page 8: ......

Page 50: ...1 40 BVW 55 1 2 3 4 5 6 7 8 9 d l s d l 1 15 Fixtures and Adjustment Equipment List ...

Page 58: ......

Page 106: ......

Page 116: ......

Page 130: ......

Page 148: ......

Page 154: ......

Page 158: ......

Page 169: ...1 9 BVW 55 P2 1 2 Fixtures and Adjustment Equipment List 1 2 3 4 5 6 7 8 9 d l s d l ...

Page 176: ......

Page 272: ......

Page 384: ......

Page 392: ......

Page 396: ...1 2 BVW 55 ...

Page 666: ......

Page 705: ......

Page 752: ......

Page 780: ......

Page 805: ......

Page 848: ......

Page 856: ......

Page 870: ......

Page 884: ......

Page 904: ......

Page 909: ...5 27 b BVW 55 5 27 b CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 12 MB 838 MB 838 ...

Page 911: ...5 27 a BVW 55 5 27 a CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 11 MB 838 MB 838 ...

Page 940: ......