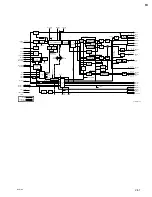

2-64

BVW-55

IC

DATA

OUT

DCLK

I/O

OE

IN

CS

IN

1

2

3

4

8

7

6

5

V

DD

V

DD

GND

CASC

OUT

C-MOS SERIAL EPROM

—TOP VIEW—

2

4

DCLK

CS

DATA

CASC

1

6

OE

3

OSCILLATOR

CONTROL

OSCILLATOR

DCLK

2

CS

4

OE

3

CLK

ENA

nRESET

ADDRESS

COUNTER

DECODE

LOGIC

EPROM

ARRAY

SHIFT

REGISTER

CASC

6

DATA

1

DATA

ADDRESS

INPUT

CS

OE

OUTPUT

CASC

INPUT/OUTPUT

DCLK

: CHIP SELECT

: OUTPUT ENABLE

: CASCADE SELECT

: CLOCK

EPC1PC8 (ALTERA)

EPF10K20TC144-3 (ALTERA)

GND GND

V

CC

IO

V

CC

INT

GND GND

V

CC

INT

109

110

115

120

125

130

135

140

144

EMBEDDED PROGRAMMABLE LOGIC DEVICE

—TOP VIEW—

72

70

65

60

55

50

45

40

37

108

105

100

95

90

85

80

75

73

1

5

10

15

20

25

30

35 36

V

CC

IO

V

CC

INT

GND GND

V

CC

IO

V

CC

INT

V

CC

IO

GND

V

CC

IO

GND

GND

V

CC

INT

V

CC

INT

GND

V

CC

IO

GND

V

CC

IO

V

CC

INT

GND

GND

V

CC

IO

GND

I

I/O

I

O

—

—

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

O

I/O

TCLK

CONF DONE

CEO

TDO

V

CC

IO

V

CC

INT

CLKUSR

I/O

I/O

I/O

RDY BSY

I/O

I/O

INT DONE

GND

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

V

CC

IO

V

CC

INT

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

TMS

STATUS

I/O

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

—

I/O

—

—

I/O

I

I/O

—

—

I/O

I/O

—

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

V

CC

IO

I/O

I/O

I/O

I/O

GND

I/O

V

CC

INT

V

CC

INT

I/O

GCLK1

I/O

GND

GND

I/O

I/O

V

CC

IO

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

V

CC

IO

I/O

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

I/O

I

—

I

I

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I

I

I

I/O

I/O

CONFIG

V

CC

INT

MSEL1

MSEL0

I/O

I/O

I/O

I/O

I/O

I/O

GND

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

V

CC

INT

V

CC

IO

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

GND

TDI

CE

DCLK

DATA0

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I

I/O

—

I

—

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

V

CC

IO

DATA7

I/O

I/O

I/O

I/O

I/O

DEV CLR

V

CC

INT

I/O

GCLK0

I/O

GND

DEV OE

GND

I/O

I/O

I/O

I/O

V

CC

IO

I/O

I/O

I/O

I/O

GND

I/O

RS

WS

CS

CS

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

HM628512BLTT-5SLZ (HITACHI)

A18

IN

A16

IN

A14

IN

A12

IN

A7

IN

A6

IN

A5

IN

A4

IN

A3

IN

A2

IN

A1

IN

A0

IN

I/O 0

I/O 1

I/O 2

GND

V

DD

A15

IN

A17

IN

WE

IN

A13

IN

A8

IN

A9

IN

A11

IN

OE

IN

A10

IN

CS

IN

I/O 7

I/O 6

I/O 5

I/O 4

I/O 3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

12

11

10

9

8

7

6

5

27

26

23

25

4

28

3

31

2

30

1

22

29

24

13

14

15

17

18

19

20

21

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

CS

WE

OE

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

INPUT

A0 - A18

CS

OE

WE

INPUT/OUTPUT

I/O 0 - I/O 7

: ADDRESS

: CHIP SELECT

: OUTPUT ENABLE

: WRITE ENABLE

: I-O DATA

C-MOS 4M (524,288

x

8)-BIT HIGH SPEED SRAM

—TOP VIEW—

Summary of Contents for BVW-55

Page 4: ......

Page 8: ......

Page 50: ...1 40 BVW 55 1 2 3 4 5 6 7 8 9 d l s d l 1 15 Fixtures and Adjustment Equipment List ...

Page 58: ......

Page 106: ......

Page 116: ......

Page 130: ......

Page 148: ......

Page 154: ......

Page 158: ......

Page 169: ...1 9 BVW 55 P2 1 2 Fixtures and Adjustment Equipment List 1 2 3 4 5 6 7 8 9 d l s d l ...

Page 176: ......

Page 272: ......

Page 384: ......

Page 392: ......

Page 396: ...1 2 BVW 55 ...

Page 666: ......

Page 705: ......

Page 752: ......

Page 780: ......

Page 805: ......

Page 848: ......

Page 856: ......

Page 870: ......

Page 884: ......

Page 904: ......

Page 909: ...5 27 b BVW 55 5 27 b CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 12 MB 838 MB 838 ...

Page 911: ...5 27 a BVW 55 5 27 a CN101 CN301 CN302 CN303 CN901 MB 838 B SIDE SUFFIX 11 MB 838 MB 838 ...

Page 940: ......