— 25 —

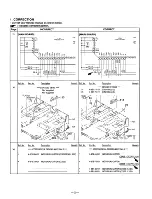

Pin Name

DV

DD

ASYE

PSSL

WDCK

LRCK

DATA

BCLK

64DATA

64BCLK

64LRCK

GTOP

XUGF

XPLCK

GFS

PFCK

C2PO

XRAOF

MNT3

MNT2

MNT1

MNT0

XTAI

XTAO

XTSL

DVss

FSTI

FSTO

FSOF

C16M

MD2

DOUT

EMPH

WFCK

SCOR

SBSO

EXCK

SUBQ

SQCK

MUTE

SENS

Pin No.

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

I/O

–

I

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

O

I

–

I

O

O

O

I

O

O

O

O

O

I

O

I

I

O

Function

Digital power supply

Asymmetry circuit ON/OFF

Audio data output mode selection input

48-bit slot D/A interface. Word clock.

48-bit slot D/A interface. LR clock.

DA 16 output when PSSL=1.48-bit slot serial data when PSSL=0

DA 15 output when PSSL=1.48-bit slot data when PSSL=0

DA 14 output when PSSL=1.64-bit slot data when PSSL=0 (Not used)

DA 13 output when PSSL=1.64-bit slot data when PSSL=0 (Not used)

DA 12 output when PSSL=1.64-bit slot data when PSSL=0 (Not used)

DA 11 output when PSSL=1.GTOP output when PSSL=0 (Not used)

DA 10 output when PSSL=1.XUGF output when PSSL=0 (Not used)

DA 09 output when PSSL=1.XPLCK output when PSSL=0

DA 08 output when PSSL=1.GFS output when PSSL=0

DA 07 output when PSSL=1.RFCK output when PSSL=0

DA 06 output when PSSL=1.C2PO output when PSSL=0 (Not used)

DA 05 output when PSSL=1.XRA0F output when PSSL=0

DA 04 output when PSSL=1.MNT3 output when PSSL=0

DA 03 output when PSSL=1.MNT2 output when PSSL=0

DA 02 output when PSSL=1.MNT1 output when PSSL=0

DA 01 output when PSSL=1.MNT0 output when PSSL=0

X'tal oscillator circuit input

X'tal oscillator circuit output (Not used)

X'tal selection input pin (GND)

Digital GND

2/3 divider output of pins 62, 63

2/3 divider output of pins 62, 63

(Not used)

16.9344 MHz output (Not used)

Digital-out ON/OFF control pin (+5V)

Digital-out output pin

Playback disc output in emphasis mode (Not used)

WFCK output

Sub-code sync output

Sub-P through Sub-W serial output (Not used)

Clock input for SBS0 read-out (GND)

Sub-Q 80-bit output

Muting selection pin

SENS output

System reset