— 39 —

— 40 —

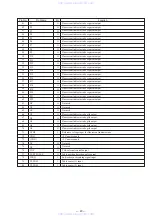

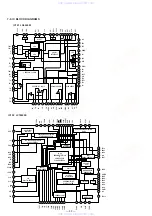

Pin No.

Pin Name

I/O

Function

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

SLOF

CV–

CV+

RFSM

RFS–

SLC

SLI

DGND

FSC

TBC

NC

DEF

CLK

CL

DAT

CE

DRF

FSS

VCC2

RFFI

VR

LF2

PH1

BH1

LDD

LDS

Sled servo off control input

CLV error signal is input from the digital signal processor

CLV error signal is input from the digital signal processor

RF output

Works together with the RFSM pin to set the RF gain and the 3T compensation constant

for the EFM signal

SLI (Slice Level Control) is output to control a data slice level of the RF waveform by the

digital signal processor

Input pin for controlling a data slice level by the digital signal processor

Digital Ground

Focus search smoothing capacitor output

TBC (Tracking Balance Control) sets a EF balance variable range

Not used

Defect detection output for a disc

Reference clock input

The 4.23 MHz of the digital signal processor is input

Microprocessor command clock input

Microprocessor command data input

Microprocessor command chip enable input

DRF (Defect RF) outputs a RF level detection

FSS (Focus Search Select) is a switching pin for the focus search mode (±search

for a reference voltage)

Servo system and digital system VCC

Reference voltage bus control is connected

Reference voltage output

Constant setting for a disc defect detection

Connected to the capacitor for the RF signal peak hold

Connected to the capacitor for the RF signal bottom hold

APC circuit output

APC circuit input

I

I

I

O

I

O

I

–

O

I

–

O

I

I

I

I

O

I

–

I

O

I

I

I

O

I

EFM : Eight to Fourteen Modulation

APC : Auto Power Control

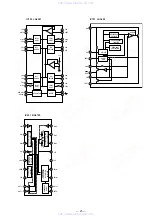

• IC102 DIGITAL SIGNAL PROCESSOR (LC78622E)

Pin No.

Pin Name

I/O

Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

DEFI

TAI

PDO

VVSS

ISET

VVDD

FR

VSS

EFMO

EFMIN

TEST2

CLV+

CLV–

V/P

HFL

TES

TOFF

TGL

JP+

JP–

PCK

FSEQ

VDD

CONT1

CONT2

CONT3

CONT4

CONT5

I

I

O

–

I

–

I

–

O

I

I

O

O

O

I

I

O

O

O

O

O

O

–

I/O

I/O

I/O

I/O

I/O

Defect detection signal (DEF) input

(Be sure to connect to 0 when not in use)

PLL

Test input

Incorporates a pull-down resistor

Be sure to connect to 0V

PLL

Phase comparison output for external VCO control

PLL

Ground for the built-in VCO

Be sure to connect to 0 when not in use

Connected to a current adjusting resistor for the PDO output

Built-in VCO power supply

Adjusts the VCO frequency range

Digital Ground

Be sure to connect to 0

Slice level control

EFM signal output

Slice level control

EFM signal input

Test input

Incorporates a pull-down resistor

Be sure to connect to 0V

Disc motor control output

3-value output available depending on the command

Rough servo/phase control automatic switching monitor output

“H”:rough servo, ‘’L”:phase servo

Tracking detection signal input

Schmidt input

Tracking error signal input

Schmidt input

Tracking OFF output

Tracking gain switching output

Raises gain when “L”

Track jump control output

3-value output available depending on the command

EFM data playback clock monitor

4.3218 MHz when phase is locked

Sync signal detection output

“H” when a sync signal detected from the EFM signal and

that generated internally coincide

Digital power supply

General purpose output 1

Performs control using a serial data command from the

microprocessor

When not in use, connect to 0V by setting to an input or set to an open

state by setting to an output

General purpose output 2

Performs control using a serial data command from the

microprocessor

When not in use, connect to 0V by setting to an input or set to an open

state by setting to an output

General purpose output 3

Performs control using a serial data command from the

microprocessor

When not in use, connect to 0V by setting to an input or set to an open

state by setting to an output

General purpose output 4

Performs control using a serial data command from the

microprocessor

When not in use, connect to 0V by setting to an input or set to an open

state by setting to an output

General purpose output 5

Performs control using a serial data command from the

microprocessor

When not in use, connect to 0V by setting to an input or set to an open

state by setting to an output

• Abbreviation

PLL : Phase Locked Loop

EFM : Eight to Fourteen Modulation

www . x ia o y u 1 6 3 . c o m

Q Q 3 7 6 3 1 5 1 5 0

9

9

2

8

9

4

2

9

8

T E L 1 3 9 4 2 2 9 6 5 1 3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299