25

I

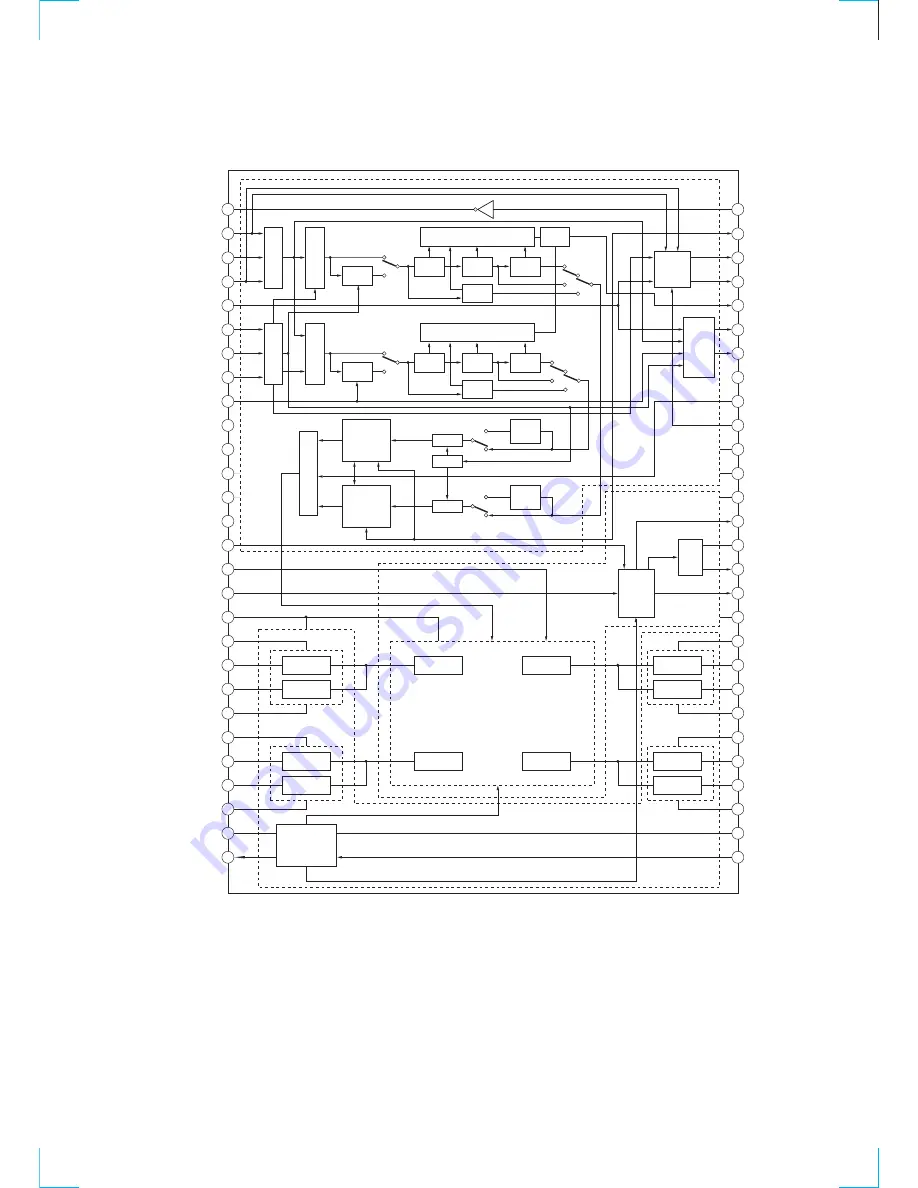

C301 CXD8735N (MAIN BOARD)

6-14. IC BLOCK DIAGRAMS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

INVI

128FsO

TEST

DINIT

MUTEL

OVFLAG

MUTER

MCKIN

DVSS1

DVDD1

64FSI

NU

XIN

XVSS

AVDDR2

AVSSR2

AVDDR1

64FSO

DVSS2

LVCKO

CKVdd

256FSO

DVDD2

R1(–)

R1(+)

R2(+)

R2(–)

AVSSR2

INVO

BCKI

DATA1

LRCKI

INIT

ATT

SHIFT

LATCH

SYSM

NU

NU

NU

DVSS1

DVDD1

XVDD

AVDDL2

L2(–)

L2(+)

AVSSL2

AVSSL1

L1(+)

L1(–)

AVDDL1

SYNC

VSUB

CKCTL

MUTE

XVDD

S/P

AT

T

MODE

AT

T

REGISTER

D/F

TIMNG

CIRCUIT

“0” DETECT

MUTE

CIRCUIT

1024Fs-CLOCK

BUFFER

Buffer(–)

)

)

Buffer(–)

PLM-R2

PLM-R1

Buffer(–)

)

)

Buffer(–)

PLM-L1

PML-L2

CLOCK

GENERA

TOR

CLOCK

BUFFER

IIR

FIR1

OVERFLOW DETECTER

OR

FIR2

FIR4

FIR3

IIR

ATT

X0.75

FIR1

OVERFLOW DETECTER

FIR2

FIR4

L.I.P

3rd order

NOISE

SHAPER

FIR3

ATT

X0.75

L.I.P

DITHER

3rd order

NOISE

SHAPER