17

17

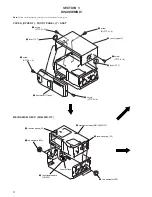

CDX-838

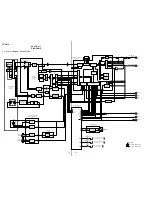

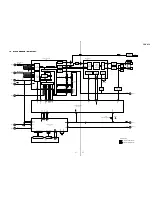

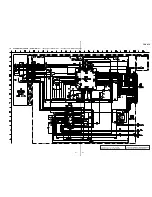

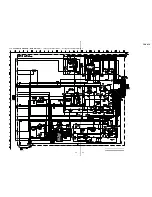

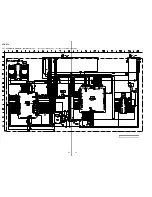

7-2.

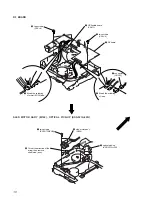

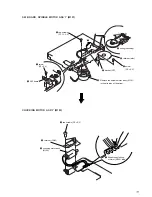

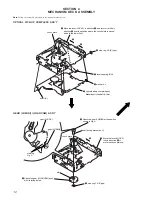

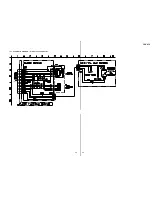

BLOCK DIAGRAM – MAIN Section –

7-2.

BLOCK DIAGRAM – MAIN Section –

11

9

12

13

7

6

5

3

8

61

47 48 46 50

29

46

76

77

25

27

45 44 49 59

16

19

17

18

20

A

B

DATA, PCMD, BCK,

LRCK, WDCK

PCMD

BCK

LRCK

WDCK

DATA

DATI

BCKI

LRCI

WDCI

4

DIN

RFCK

WFCK

XROF

C4M

C4M

XROI

SCOR

RFCK

GTOP

RFCK, GTOP, WFCK,

C4M, XROF

WFCK

WFCK

2

31, 30, 33, 32

1, 2, 24, 25

25 – 22, 40 – 36, 27

9 – 12, 14 – 18, 5

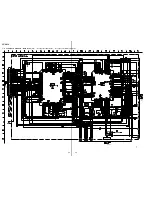

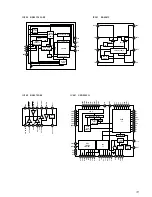

DSP

INTERFACE

DATA

LINKING

CONTROL

SELECTOR

D-RAM INTERFACE

READ/WRITE

BASE

COUNTER

VWA

ADDRESS MONITOR

CPU INTERFACE

SDTI

1

GRST

60

GSCR

SCK

DATA

GRSCOR

79

CSI

78

CSO

77

7 6 5

CCLK

CSI

76

REQ

74

BUSY

4 56

BUSY

CCLK

SCOR

WFCK

8

9

SCLK

SSI

SDTI

41 42 28 26

CLOCK

SDTO

XLT

XRDE

XWRE

XSOE

XQOK

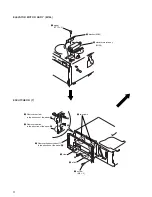

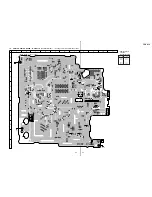

SYSTEM CONTROLLER

IC201 (2/3)

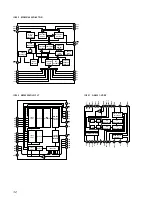

D/A CONVERTER

IC601

05

CD TEXT DECODER

IC501

D-RAM

IC402

S-RAM

IC502

A0 – A9

D1 – D4

XTAI

TIMING

GENERATOR

D/A

CONVERTER

INTERFACE

SERIAL

INPUT

INTERFACE

DE-EMPHASIS

CONTROL

CPU

INTERFACE

CLOCK OSC/

DIVIDER

CLOCK

BUFFER

IC603

MUTING

CONTROL SWITCH

Q601, 602

LOW-PASS

FILTER

IC602 (1/2)

MUTING

Q603

LOW-PASS

FILTER

IC602 (2/2)

PWM

INTER-

POLATOR,

∆Σ

MODULATOR

DATA

D OUT

BCK

LRCK

DATA

BCK

LRCK

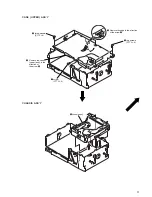

D-RAM CONTROLLER

IC401

DIGITAL

OUT

BUFFER

IC604

(Page 16)

D

SCLK

IC503

SBSO

(Page 16)

E

(Page 16)

G

SCOR

(Page 16)

F

DATA, CLOCK

(Page 16)

H

(Page 16)

(Page 16)

C

C16M

(Page 16)

I

(Page 18)

J

BU CHECK

(Page 18)

RESET

XRST

35

29

34

28

22

3

23

4

20 27

62 63

XRAS

XCAS

XWE

XOE

XRAS

D1 – D4

A0 – A9

11 – 13, 15 – 19

10 – 3, 25, 24, 21, 23, 2, 26, 1

11 – 18, 64 – 69, 74

DO0 – DO7

20 – 27

DATA0 – DATA7

A0 – A14

ADD0 – ADD14

XCAS

XWE

CE

CE

WE

WE

XOE

ESPXLT

XRDE

XWRE

XSOE

XQOK

GRSRT

CSO

REQ

OPTICAL

TRANSCEIVER

IC801

SW801

(ANALOG/DIGITAL SELECT)

BUCK

D501

X601

16.9344MHz

AOUTL

AOUTR

A/D.SW

XT

AL

EXT

AL

EMP

DFS

PD

EMP

ML

D/A.RESET

XTO

XTI

56

28

78

12

11

6

44

45

A.MUTE

43

47

RESET

75

4

5

18

17

8

7

9

X501

10MHz

30

29

MUTING

Q604

R

L

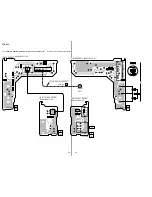

CN901 (1/2)

ANALOG OUT

IC801

DIGITAL OUT

RST

ANALOG

DIGITAL

GTOP

RESET

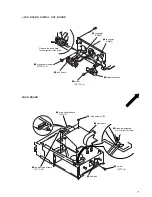

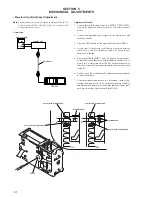

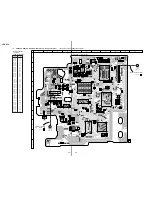

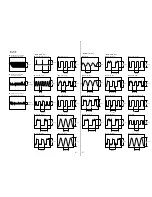

• SIGNAL PATH

: CD PLAY (ANALOG OUT)

: CD PLAY (DIGITAL OUT)