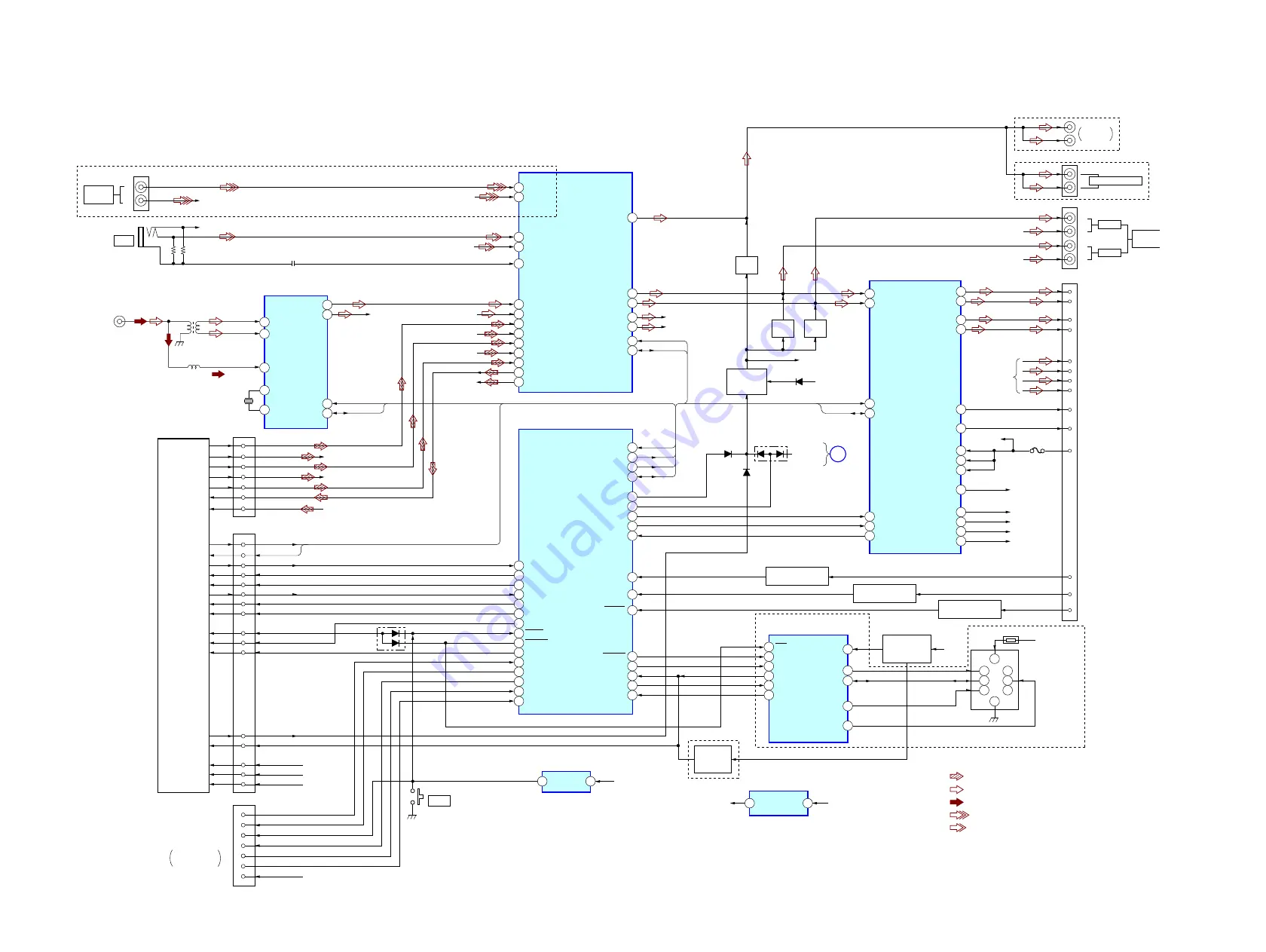

CDX-GT650UI/GT700UI/GT707UI

CDX-GT650UI/GT700UI/GT707UI

15

15

2

4

11

12

24

23

18

6

8

9

19

21

7

5

17

27

4

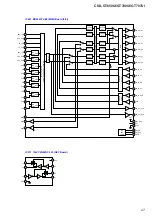

TXD

SP_CLK

SP_DATA

RXD

WAKE_UP

Z_MUTE

CD_ON

CDM_ON

SYS_RST

EJECT_OK

VBUS_ON

A_ATT

BU_CHECK

VDD_3.3V

BU_3.3V

DR_6V

R-CH

R-CH

R-CH

R-CH

R-CH

R-CH

BU+3.3V

SERVO+3.3V

R-CH

R-CH

BU +3.3V

14

D731

ELECTRONIC VOLUME

IC401

J1

(ANTENNA)

PHASE LOCKED LOOP

(PLL)

IC001

L6

FM MIX

L2

CN701 (1/2)

CN402

CD

MECHANISM

UNIT

(MG-101P)

(1/2)

I2C BUS CONTROLLED

POWER AMP/MULTIPLE

VOLTAGE REGULATOR

IC301

SYSTEM CONTROL

IC501 (1/2)

RESET

IC403

CN301

AU_IN_FR

AU_IN_RL

AU_IN_RR

AU_IN_SUB

AU_OUT_LCH

AU_OUT_RCH

R-CH

R-CH

R-CH (FRONT)

R-CH (REAR)

BATT

R-CH

AU_FR_CH

AU_FL_CH

AU_RR_CH

AU_RL_CH

AU_SUB_CH

AU_IN_RCH

AU_IN_LCH

J901

L

R

-1

-2

AUX

J403 (1/2)

X1

4MHz

BUS

AUDIO IN

S401

RESET

US,CND

MODEL

US,CND MODEL

R-CH

BATT

R-CH

AUDIO+8.5V

SERVO+3.3V

MECHA+6V

PANEL+B

7

10

12

11

16

1

9

2

4

3

6

I2C_SCK

I2C_SIO

I2C_SCK

I2C_SIO

I2C_SCK

I2C_SIO

I2C_SCK

I2C_SIO

FL+

FL–

L

R

RL+

RL–

FR+

FR–

RR+

RR–

ANT-REM

BATT

ACC

MUTE

Q405

MUTE DRIVE

Q407,409

13 RST

12 BUS_IN

11 CLK_IN

10 BU_CHECK

EXCEPT US,CND MODEL

ACC DETECT

Q301

MUTE

Q404

5

AMP-REM

13

TEL-ATT

TEL-ATT DETECT

Q303

14

ILL

ILL DETECT

Q302

REAR

SP_CLK

SP_DATA

BUS INTERFACE

IC801

D401

D403

D404

D402

FU601

B.U+5V

FRONT

R-CH

L

J403 (2/2)

R

-3

-1

-2

-4

-5

-6

AUDIO

OUT

MUTE

Q402

BU+3.3V

BATT

5

6

8

4

2

3

1

BATT

CN801

(BUS CONTROL IN)

TH801

7

BACK-UP

CHECK

Q802,D806,807

MECHA+6V

BU3.3V

6

3

FLASH_W

BUSY

7

CLK

2

RESET

TXD

4

1

5

RXD

CN501

FLASH

PROGRAMMING

BU+3.3V

B.U+5V

BACK-UP

CHECK

Q807,808

US,CND MODEL

SUB OUT

(MONO)

EXCEPT US,CND MODEL

J403 (1/2)

13

R-CH

12

9

8

6

R-CH

SUB OUT (MONO)

S

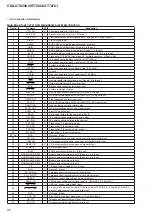

LJQDO

P

DWK

A

EEUHYLDWLRQ

R-CH

LV

RPLWWHG

GXH

WR

VDPH

DV

L-CH.

AM

RU

MW

: CD

CND : C

DQDGLDQ

PRGHO

: FM

: BUS AUDIO

: AUX

SECTION 4

DIAGRAMS

4-1. BLOCK DIAGRAM – MAIN Section –