13-32

13-32

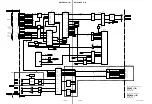

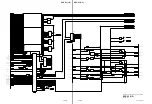

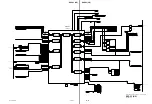

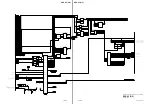

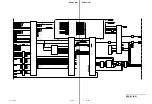

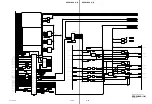

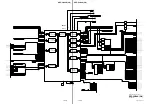

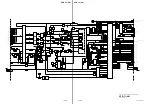

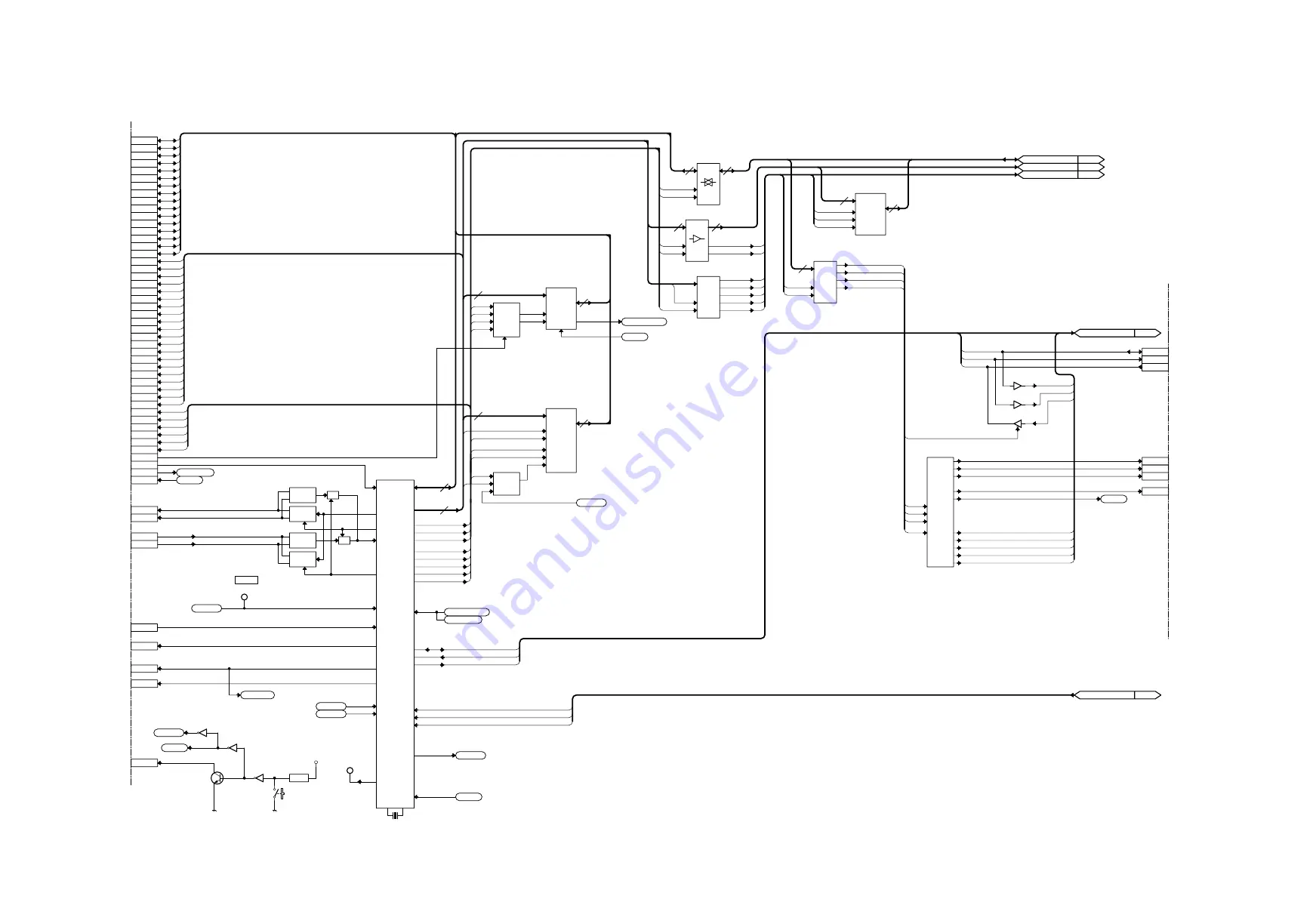

DSR-1800/P/1600/P

SSP-23 (3/5)

SSP-23 (3/5)

System/servo/analog audio input

.

output process

SSP-23 (3/5)

LOT NO. 064-

TP503

SY_INT

+5V

S500

Q500

IC506

IC517

IC517

GND

GND

IC509

IC509

IC510

2

1

18

SY_SIO

SY_C_BUS

SY_A_BUS

SY_D_BUS

WRL

RD

WRH

RD

WRL

CS0

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

CS1

RD

CS0

CS3

CS2

WRH

WRL

RD

IRQ5

IRQ6

IRQ7

CS0

CS1

CS2

CS3

CS6

WRL

A16

WRH

A0

CS2

CS6

WRL

RD

CS6

RD

WRL

RD

CS10

CS12

WRL

0

1

2

3

SY_SO

SY_SI

SY_SCK

SY_SCK

SY_SO

SY_SO_3V

SY_SI

SY_SI_3V

3

3

2

1

0

C1P_MCS

C1P_SCS

DV_CS

DIF_CS

SDI_CS

SY_SCK_3V

TXD1

RXD1

AD0-15

A0-21

PA15

IRQ5

IRQ6

PA14

RD

WRL

WRH

RESET

PA10

IRQ7

PA12

PA8

PA7

PB1

IC501

SY/SP CPU

1-3,5-12

14,16-19

16

20-23,25-31

33-37,39-40

42-45

22

57

55

56

19

A1-19

28

11

1-8

16-25

48

IC519

FLASH MEMORY

A0-18

WE

OE

D0-15

29-36

38-45

16

1-9

1-10

1-11

1-12

1-13

1-14

1-15

1-16

1-17

1-18

1-19

1-20

1-21

1-22

1-23

1-24

1-25

1-26

1-27

1-28

1-29

1-30

1-31

1-32

1-33

1-34

1-35

1-36

1-37

1-38

1-39

1-40

1-41

1-42

1-43

1-44

1-45

1-46

1-47

1-48

1-49

1-50

7-10,13-16

29-32,35-38

WE

16

D0-15

OE

1-5,18-21

24-27,42-44

IC503

A1-16

CS

16

SRAM

A0-15

D0-15

6

41

17

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

JIG

96

58

95

62

60

JIG

1-8

1-7

JIG

1-6

JIG

JIG

1-5

H-JIG_EXIST

DOWN/UP

L_RESET

L_RESET

12

RY/BY

SV_FLASH_RY/BY

SY_JIG_RY/BY

X500

19.6608MHz

72

71

XTAL

EXTAL

SY_JIG_RY/BY

67

FPGA_DONE

65

98

99

100

L_RESET

76

84

13

13

A0-12

3

4

IC511,513

2-9

11-18

SY_FLASH_RY/BY

68

RM_TX(+)

RM_TX(-)

RM_RX(+)

RM_RX(-)

RS-422

DRIVER

RS-422

RECEIVER

RS-422

RECEIVER

RS-422

DRIVER

SW

SW

IC514

IC514

IC512

IC512

46

CS0

CS1

47

48

CS2

CS3

49

53

CS6

PA13

66

FPGA_INIT

102-67

H_MOTOR_OFF

86

PB3

PRE-45,201-33

90

102-131

PB6

IF-820,104-44,HP-108,109-12

PB7

102-148

91

H_AUDIO_OUT_MUTE

IF-820,201-41

H_JC_RESET

WE

DECODER

FPGA_DONE

IC500,504

IC517

BHE

39

40

BLE

OE/WE

DECODER

IC500,516

IC517

SY_SYS_CK

CK

69

RESET

IC505

PRE-45,201-32

KY-484,108-2,DR-428,303-4

IF-820,103-10

102-130

PLD_RESET

L_CPU_RESET

L_RESET

A0-12

D0-7

8

11-18

2-9

IC515

1

19

D0-7

8

G

DIR

1-3

4

5

IC518

G

G

DECODER

A18-20

A21

15

14

13

12

11

WRL

RD

CS8

CS9

CS10

CS11

CS12

IC600

2-10,21

23-25

8

22

27

11-13

15-19

D0-7

OE

WE

NVRAM

A0-12

20

CE

13

A0-12

D0-7

5

6

9

CLK

11

CLK_EN

D0-7

IC603

OUTPUT

LATCH

2

1

8

97

SCK0

RXD0

93

94

TXD0

IF-820,103-8,KY-484,108-6

KY-484,108-3

102-134

102-128

KY_CS

102-127

102-126

DECODER

IC507,508

NSG_CS

IF-820,103-4

102-124

102-122

NCG_CS

102-132

FPGA_CS

17

16

102-146

102-144

102-143

102-142

H_JC_RESET

IF-820,103-7,KY-484,108-4

IF-820,103-6,KY-484,108-5

IF-820,103-2

IF-820,104-80

VPR_AD_CS

002

002

002

002

002

TP501

P-TRKT

P-TRKT

83

PB0

IF820,103-3

102-123

NSG OE

Summary of Contents for DSR-1600P

Page 6: ......

Page 7: ...5 J DSR 1800 P 1600 P V2 ...

Page 8: ...6 J DSR 1800 P 1600 P V2 ...

Page 24: ......

Page 25: ...12 1 J DSR 1800 P 1600 P Section 12 Spare Parts and Optional Fixtures 12 1 ...

Page 26: ......

Page 172: ......

Page 176: ......

Page 190: ......

Page 198: ......

Page 216: ......

Page 220: ......

Page 229: ......

Page 234: ......

Page 238: ......

Page 252: ......

Page 256: ......

Page 260: ......

Page 268: ......

Page 276: ......

Page 278: ......

Page 284: ......

Page 294: ......

Page 316: ......

Page 366: ......

Page 379: ......

Page 385: ......

Page 388: ......

Page 396: ......

Page 404: ......

Page 420: ......

Page 426: ......

Page 440: ......

Page 462: ......

Page 466: ......

Page 467: ......