11-13

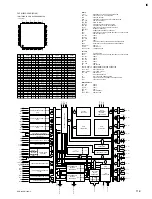

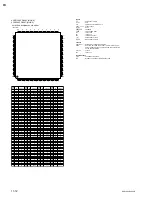

DSR-1800/P/1600/P

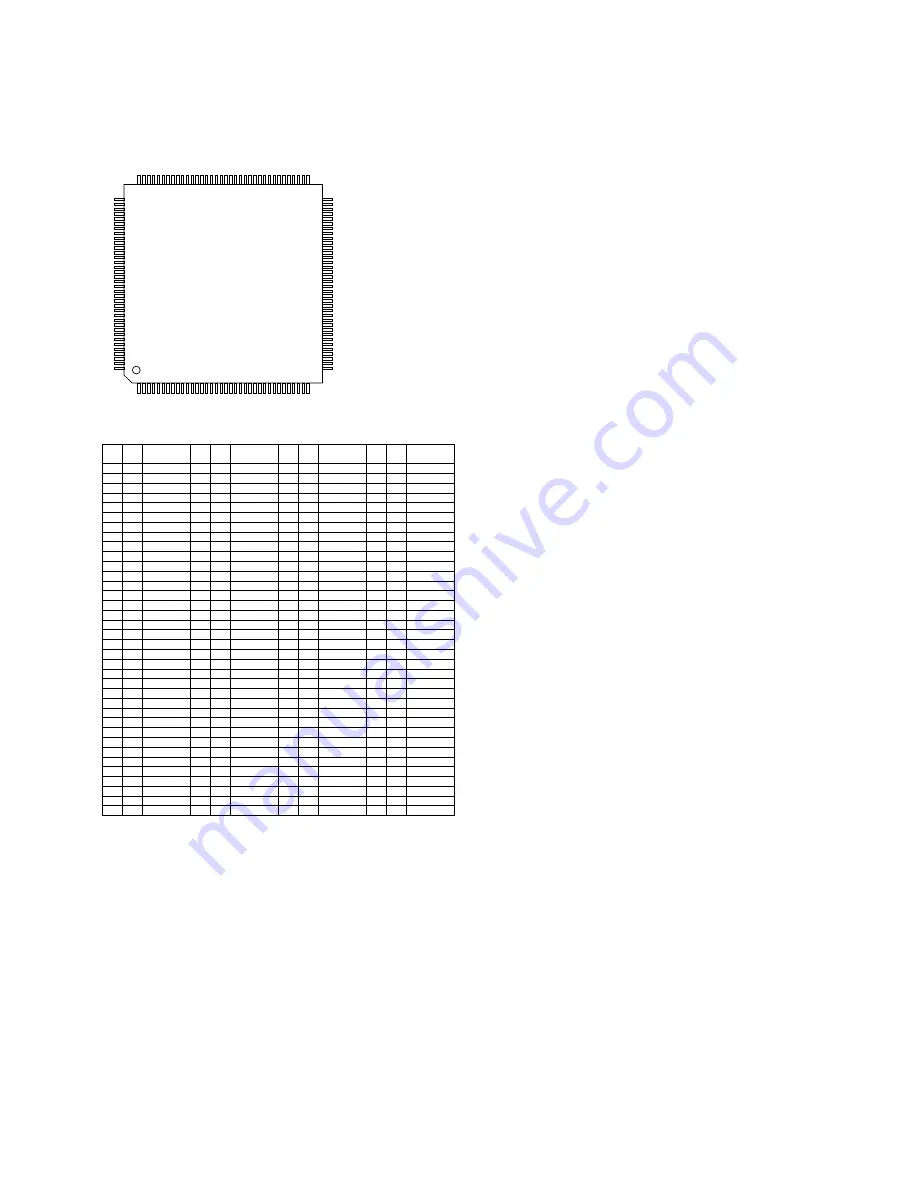

XCS10XL-4TQ144C (XILINX)

109

110

115

120

125

130

135

140

144

FIELD PROGRAMMABLE GATE ARRAY

—TOP VIEW—

72

70

65

60

55

50

45

40

37

108

105

100

95

90

85

80

75

73

1

5

10

15

2

0

2

5

3

0

3

5

3

6

—

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I

—

I

GND

I/O, PGCK1

I/O

I/O

I/O

I/O, TDI

I/O, TCK

GND

I/O

I/O

I/O, TMS

I/O

I/O

I/O

I/O

I/O

GND

V

CC

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

I/O, SGCK2

NC, M1

GND

MODE, M0

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

—

I

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

V

CC

NC,

PWRDWN

I/O, PGCK2

I/O (HDC)

I/O

I/O

I/O

I/O (

LDC

)

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O (

INIT

)

V

CC

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

I/O, SGCK3

GND

DONE

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

—

I

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

V

CC

PROGRAM

I/O (D7)

I/O, PGCK3

I/O

I/O

I/O (D6)

I/O

GND

I/O

I/O

I/O (D5)

I/O

I/O

I/O

I/O (D4)

I/O

V

CC

GND

I/O (D3)

I/O

I/O

I/O

I/O (D2)

I/O

I/O

I/O

GND

I/O (D1)

I/O

I/O

I/O

I/O (D0, DIN)

I/O, SGCK4 (DOUT)

CCLK

V

CC

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

O

—

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

—

O, TDO

GND

I/O

I/O, PGCK4

I/O

I/O

I/O (CS1)

I/O

NC

GND

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

V

CC

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

I/O

I/O

I/O, SGCK1

V

CC

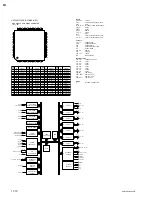

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

INPUTS

CS1

D0 - D7

DIN

M0, M1, MODE

PROGRAM

PWRDWN

TCK

TDI

TMS

OUTPUTS

HDC

LDC

O, TDO

INPUTS/OUTPUTS

CCLK

DONE

I/O

INIT

PGCK1 - PGCK4

SGCK1 - SGCK4

OTHER

NC

: SERIAL ENABLE

: DATA

: DATA INPUT RECEIVING DATA

: MODE

: CONFIGURATION MEMORY

: POWER DOWN

: TEST CLOCK

: TEST DATA INPUT

: TEST MODE

: HIGH DURING CONFIGURATION

: LOW DURING CONFIGURATION

: TEST DATA OUTPUT

: CONFIGURATION CLOCK

: COMPLETION OF THE CONFIGURATION PROCESS

: INPUT AND OUTPUT

: INTERNAL CLEARING/INTERNAL WAIT

: PRIMARY GLOBAL INPUT

: SECONDARY GLOBAL INPUT

: NO CONNECTION

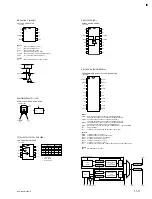

IC

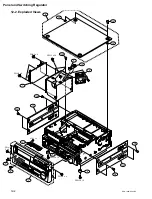

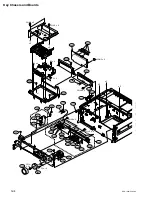

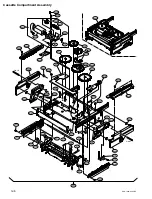

Summary of Contents for DSR-1600P

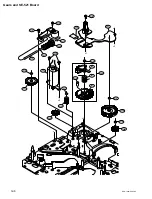

Page 6: ......

Page 7: ...5 J DSR 1800 P 1600 P V2 ...

Page 8: ...6 J DSR 1800 P 1600 P V2 ...

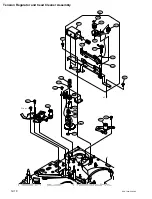

Page 24: ......

Page 25: ...12 1 J DSR 1800 P 1600 P Section 12 Spare Parts and Optional Fixtures 12 1 ...

Page 26: ......

Page 172: ......

Page 176: ......

Page 190: ......

Page 198: ......

Page 216: ......

Page 220: ......

Page 229: ......

Page 234: ......

Page 238: ......

Page 252: ......

Page 256: ......

Page 260: ......

Page 268: ......

Page 276: ......

Page 278: ......

Page 284: ......

Page 294: ......

Page 316: ......

Page 366: ......

Page 379: ......

Page 385: ......

Page 388: ......

Page 396: ......

Page 404: ......

Page 420: ......

Page 426: ......

Page 440: ......

Page 462: ......

Page 466: ......

Page 467: ......