DVP-CX777ES

68

68

R021

R620

R

663

R

664

R

665

R675

R676

R677

R

6

78

R

679

R

6

80

R

681

R

682

R

683

R674

R686

R687

C626

C635

C624

C625

C627

C628

C629

C631

C636

C637

C634

C639

C638

C633

C630

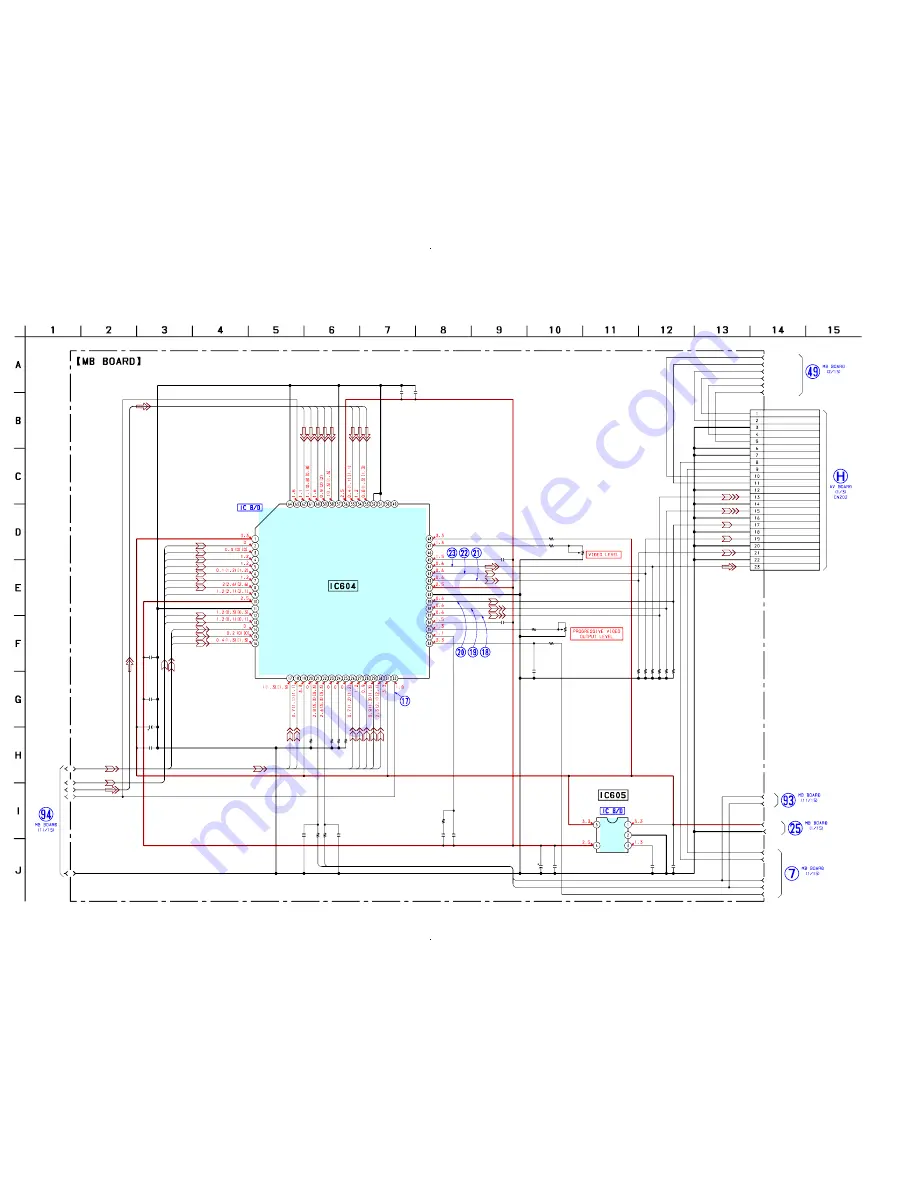

IC604

IC605

RV601

RV602

CN601

C640

C632

10k

0

0

0

0

2.7k

2.7k

100

300

30

0

300

300

300

300

680

100

100

100

6.3V

100

6.3V

0.22

0.22

0.22

470p

470p

0.1

0.22

0.001

0.22

0.01

0.22

820p

3900p

ADV7310KST

TK11125CSCL-G

1k

1k

23P

0.1

0.1

F1

F2

F3

F4

F5

SCL

SDA

WIDE

XRST

IPSW

+3.3V

GND

V-MUTE

V-OFF

RX

TX

SLINK

SIRCS_MODE

SCL

SDA

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

Y9

CBCR0

CBCR1

CBCR2

SCL

SDA

P00

P01

P02

P03

P04

P05

P06

P07

CBCR3

CBCR4

CBCR5

CBCR6

CBCR7

CBCR8

CBCR9

SDA

SCL

SIRCS_MODE

GND

TX

RX

GND

GND

IPSW

V-OFF

V-MUTE

GND

GND

Y/G

GND

Y

GND

C

V

GND

WIDE

GND

VIN

VOUT

CONT

GND

NOISE

VDD_IO

P_Y(0)

P_Y(1)

P_Y(2)/SCANEN

P_Y(3)/TESTMODE

P_Y(4)

P_Y(5)

P_Y(6)

P_Y(7)

VDD

GND

P_Y(8)

P_Y(9)

P_C(0)

P_C(1)

P_C(2)

P_C(3)

P_C(4)

SPI_12C_EN

ALS8

SDA

SCLK

P_HSYNS

P_VSYNC

P_BLANK

P_C(5)

P_C(6)

P_C(7)

P_C(8)

P_C(9)

R

TC/SCRESET/TR

CLKIN

GND_IO

CLKIN_2

S(9)

S(8)

S(7)

S(6)

S(5)

GND

VDD

S(4)

S(3)

S(2)

S(1)

S(0)

S_HSYNC

S_VSYNC

S_BLANK

RSET1

VREF

COMP1

V

Y

C

VAA

GND

Y/G

CB/R

CR/B

COMP2

RSET2

EXT_LF

RESET8

(12/15)

D/A CONVERTER

+2.5V REGULATOR

S-LINK

CR/B

CB/R

7-18. SCHEMATIC DIAGRAM – MB Board (12/15) –

•

See page 94 for Waveforms.

•

See page 98 for IC Block Diagrams.

(Page 67)

(Page 58)

(Page 83)

(Page 67)

(Page 57)

(Page 57)