DVP-NS305/NS310/NS315/NS405/NS410/NS415

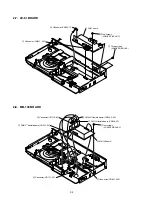

3-7

3-8

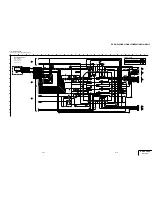

3-4. SYSTEM CONTROL BLOCK DIAGRAM

17

62

67

48

18

57

82

63

56

36

9

15

10

20

76

51

83

7

39

26

27

38

25

7

6

5

70

58

71

46

16

81

47

60

61

49

50

8

7

1 – 5 102 – 109 111 – 118 120

85 – 100

14

MB-103 BOARD (3/4)

(SEE PAGE 4-25 to 4-28)

IC104

SYSTEM

CONTROL

IC103

PLL

IC101

EEPROM

HD 0 – 15

HA 0 – 21

SIGNAL PROCESSOR

(SEE PAGE 3-5)

XARPIT

XARPCS

XWAIT

HA0

–

21

HA1

–

20

HD0

–

15

HD0

–

15

CSOX

SO0

SCO

SI0

INTERFACE

CONTROL

(SEE PAGE 3-13)

SI0

SO0

SC0

XIFCS

XIFBUSY

XFRRST

MAMUTE

XRST

INT4

XFRRST

XIFCS

MAMUTE

48/44.1k

54

53

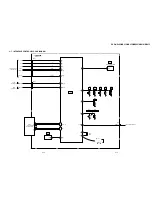

X101

16.5MHz

XDRVMUTE

INT2

WIDE

CS5X

CKSW1

XDRVMUTE

XSDPIT

OCSW1

XLDON

XSDPCS

CKSW1

DREQ0

INTO

DACK0

CS2X

CS3X

DREQ1

DACK1

DREQ0

XAVDIT

DACK0

XAVDCS2

XAVDCS3

DREQ1

DACK1

VIDEO

(SEE PAGE 3-9)

SIGNAL PROCESSOR

(SEE PAGE 3-5)

RF/SERVO

(SEE PAGE 3-4)

16

33MARP

512FSAVD

X102

27MHz

33-1OUT

FSEL

512FS6CH

512FS2CH

TRST

29

SO1

SO1

30

SC1

SC1

79

XDACS

XDACS

INT1

CS4X

XWAIT

35

XRST

XRST

XRST

XRD

XWRH

512-2OUT

512-1OUT

XTI

XTO

3

27MAVD

27-1OUT

X1

X2

HD 0 – 15

HA 0 – 21

XRD

XWRH

3

CN101

5

6

8

4

1

CN601 (2/3)

2

WP

SCL

SDA

OCSW1

SCL

SDA

WP

WIDE

XARPRST

SI0

SO0

SC0

XIFCS

IFBSY

TRST

WIDE

AUDIO

(SEE PAGE 3-11)

HA 0 – 21

HD 0 – 15

IC106

FLASH

29.5nsec

3

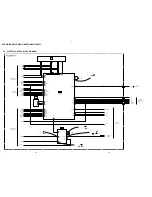

IC103

qg

5.0Vp-p

37nsec

2

IC103

3

5.5Vp-p

40.8nsec

5.0Vp-p

4

IC103

9q;

37nsec

1

IC103

8

4.4Vp-p

60.6nsec

5

IC104

tf

1.8Vp-p

Summary of Contents for DVP-NS305

Page 7: ... 7 6 Set complete Fig 6 ...

Page 8: ... 8 MEMO ...

Page 32: ...2 8E MEMO ...

Page 42: ...3 20E MEMO ...

Page 64: ...DVP NS305 NS310 NS315 NS405 NS410 NS415 4 44E MEMO ...

Page 88: ...6 22E MEMO ...