5-2E

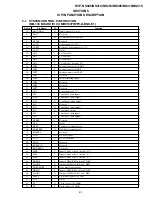

Pin No.

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85Å[92

93-100

101

102-109

110

110-118

119

120

Pin Name

VCC

CKSW1

OCSW1

CS0X

CS1X

CS2X

CS3X

CS4X

CS5X

VCCI

CS6X

CX7X

XWAIT

BGRNTX

BRQ

XRD

XWRH

XWRL

NMIX

VCCI

VSS

XFRRST

CPUCK

OCSW2

XDACS

TRMÅ|

48/44.1K

WIDE

MAMUTE

SRAMWE

HD0-HD7

HD8-HD15

VSS

HA0-HA7

VCC

HA8-HA15

VSS

HA16

I/O

–

I

I

O

–

O

O

O

O

–

–

–

I

I

I

O

O

–

I

–

–

I

O

–

O

–

O

O

O

–

I/O

I/O

–

O

–

O

–

O

Function

Power supply (+3.3 V)

Chuck sensor input

Tray sensor input

Chip select signal output (for external ROM)

Not used

Chip select signal output (for AV DEC)

Chip select signal output (for AV DEC)

Chip select signal output (for ARP)

Chip select signal output (for SERVO DSP)

Power supply (+1.8 V)

Not used

Not used

Wait signal input

Test terminal (fixed at “H”)

Test terminal (fixed at “L”)

Read timing signal output

High order byte write timing signal output

Not used

Fixed at “H”

Power supply (+1.8 V)

GND

Reset signal input from IF CON

CPU clock signal output

Not used

Chip select signal output to DAC (2 CH)

Not used

PLL FS control signal output

LD mute signal output

Audio mute signal output

Not used

Data bus D0 to D7 (16 bits only)

Data bus D8 to D15 (16 bits) and D0 - D7 (8 bits)

GND

Address bus A00 to A07

Power supply (+3.3 V)

Address bus A08 to A15

GND

Address bus A16

Summary of Contents for DVP-NS305

Page 7: ... 7 6 Set complete Fig 6 ...

Page 8: ... 8 MEMO ...

Page 32: ...2 8E MEMO ...

Page 42: ...3 20E MEMO ...

Page 64: ...DVP NS305 NS310 NS315 NS405 NS410 NS415 4 44E MEMO ...

Page 88: ...6 22E MEMO ...