26

26

DVP-NW50

DVP-NW50

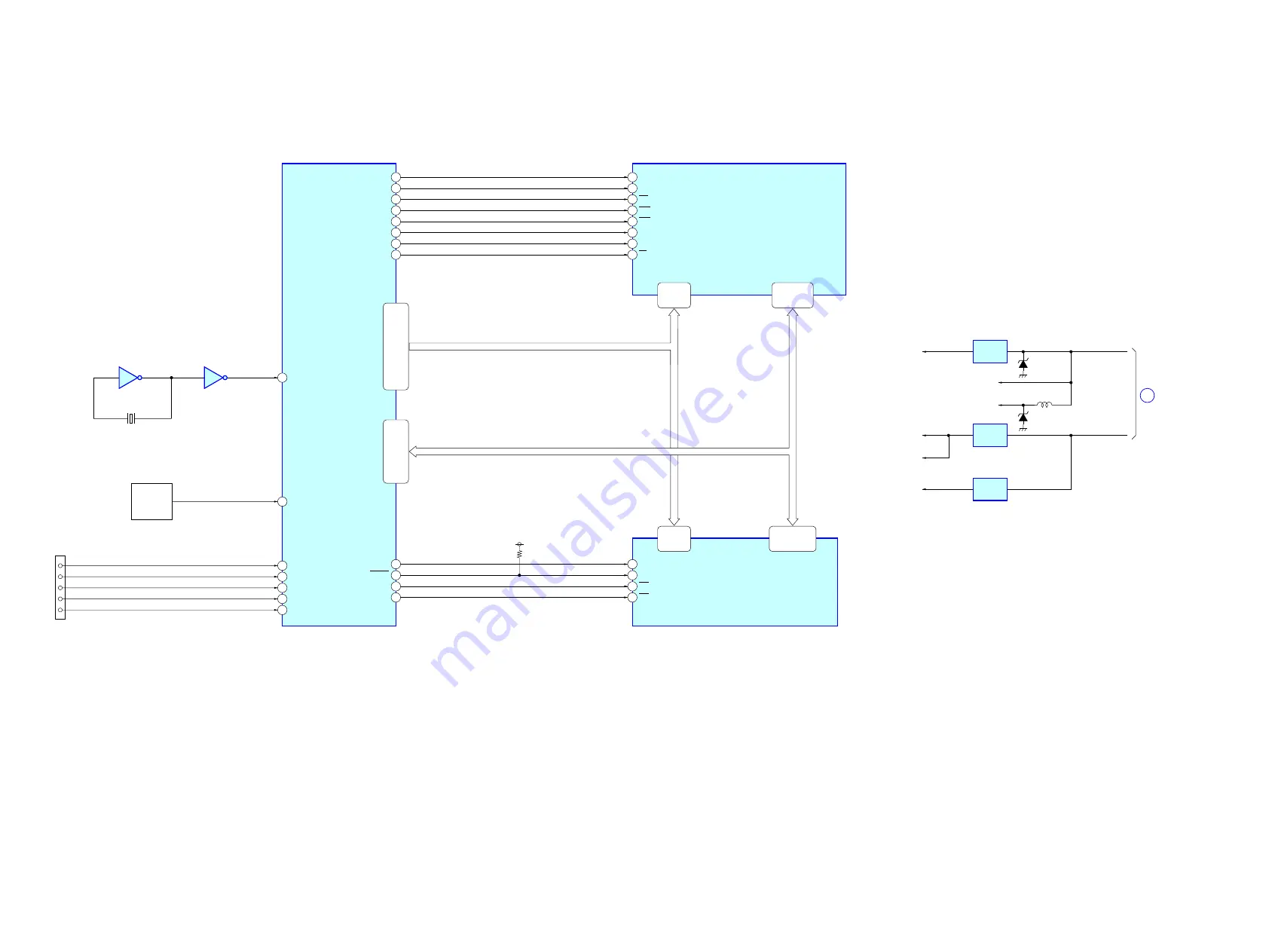

6-4. BLOCK DIAGRAM — MAIN (3) SECTION —

U1 (3/3)

SYSTEM CONTROLLER

U22

U15

D15

L11

RVDD (3.3V)

3.3VDC

CVDD (1.8V)

CD$VCC3V

D14

14VDC

VCC5V

CD$VCC5V

12T05VCC

VCC9V

RVDD

4

2

4

2

JTAG PART

J3

X1

14.7456MHz

Y1

36.768KHz

48,46

44,40

38,36

32,30

73,71

69,65

63,61

59,55

74,72

70,68

64,62

60,56

47,45

43,39

37,33

31,29

20,21

22-26

29-36

2,4,5,7,8,10,11

13,42,44,45,47

48,50,51,53

28 - 17

13 - 10

33,35,38,40,44

46,49,51,34,36

ADDRES BUS

DATA BUS

EP$RD

EP$WR