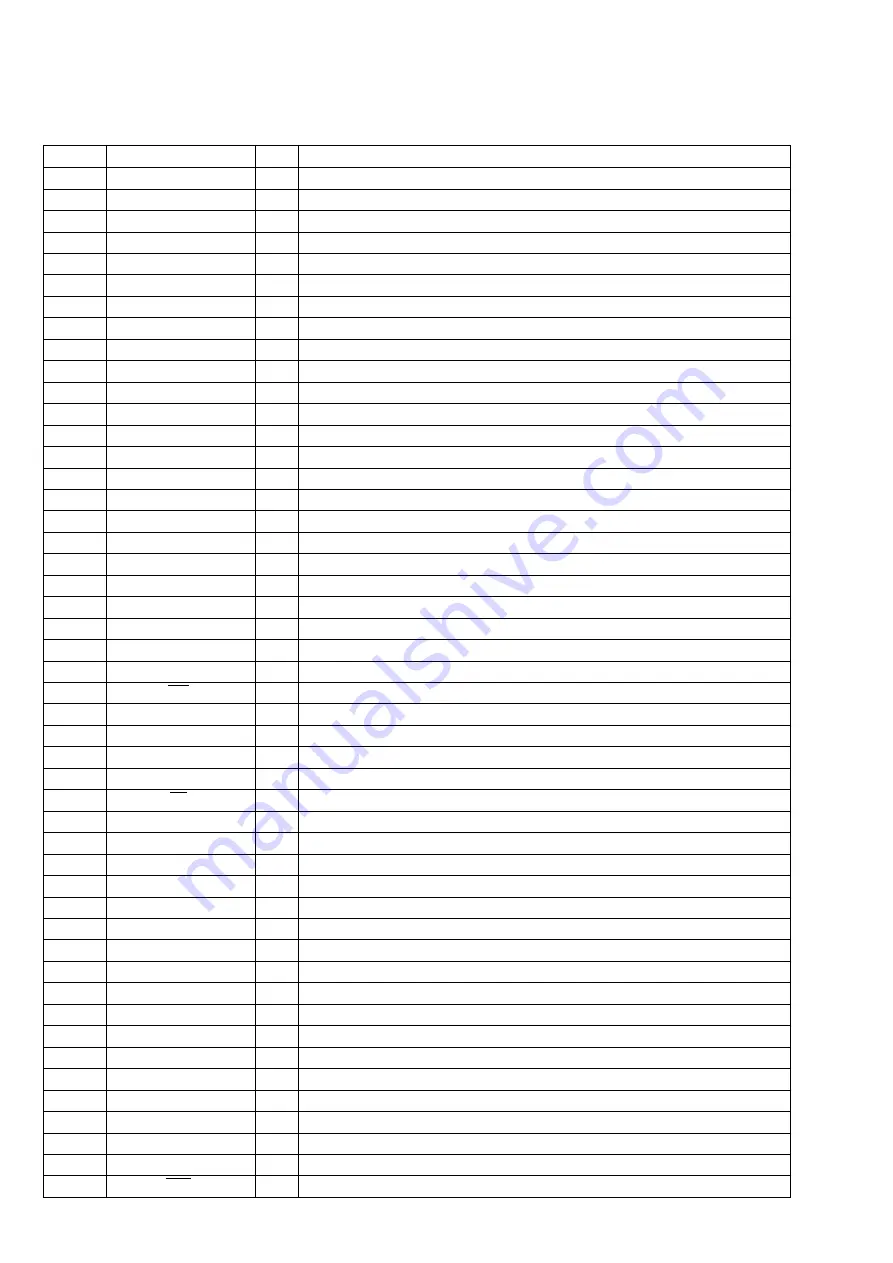

54

DVP-NW50

Pin No.

Pin Name

I/O

Description

1

MDIO

I/O

Management independent interface (MII) data input/output

2

MDC

I

MII clock input

3

RXD3

O

MII receive data output

4

RXD2

O

MII receive data output

5

RXD1

O

MII receive data output

6

RXD0

O

MII receive data output

7

VDDIO

—

Digital IO 2.5/3.3V tolerant power supply

8

GND

—

Ground terminal

9

RXDV

O

MII receive data valid output

10

RXDCLK

O

MII receive clock output

11

RXER

O

MII receive error output

12

GND

—

Ground terminal

13

VDDC

—

Digital core 2.5V only power supply

14

TXER

I

MII transmit error input

15

TXCLK

O

MII transmit clock output

16

TXEN

I

MII transmit enable input

17

TXD0

I

MII transmit data input

18

TXD1

I

MII transmit data input

19

TXD2

I

MII transmit data input

20

TXD3

I

MII transmit data input

21

COL/RMII

O

MII collision detect output

22

CRS/RMII

O

MII carrier sense output

23

GND

—

Ground terminal

24

VDDIO

—

Digital IO 2.5/3.3V tolerant power supply

25

INT

O

Management interface (MII) interrupt out

26

LED0/TEST

O

Link/Activity LED output

27

LED1/SPD100

O

Speed LED output

28

LED2/DUPLEX

O

Full-duplex LED output

29

LED3/NWAYEN

O

Collision LED output

30

PD

I

Power down signal input

31

VDDRX

—

Analog 2.5V power supply

32

RX–

I

Receive input

33

RX+

I

Receive input

34

FXSD/FXEN

—

Fiber mode enable / signal detect in fiber mode (not used)

35

GND

—

Ground terminal

36

GND

—

Ground terminal

37

REXT

I

External resistor (6.49kW) connects to REXT and ground

38

VDDRCV

—

Analog 2.5V power supply

39

GND

—

Ground terminal

40

TX–

O

Transmit outputs

41

TX+

O

Transmit outputs

42

VDDTX

—

Transmitter 2.5V power supply

43

GND

—

Ground terminal

44

GND

—

Ground terminal

45

XO

O

Xtal feedback

46

XI

I

Crystal oscillator input

47

VDDPLL

—

Analog pll 2.5V power supply

48

RST

I

Reset signal input

MAIN BOARD U26 KSZ8721BL (PHYSICAL LAYER TRANSCEIVER)