6-3

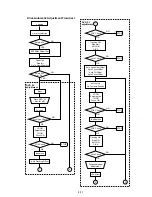

(5-4) Servo DSP Download

DSP (IC506) code area ROM/RAM discrimination

RAM: Program download

→

Revision data read

ROM: Revision data read

Error 04: Data read error

13: DSP data not ready

For the Mask ROM, no download can be executed. Download is

possible for the RAM only. ROM/RAM is discriminated by the

DBUSY signal of DSP (IC506) pin

4

after hardware reset. The

diagnosis provides exclusive download flag.

For this flag, download not executed

: 0

download already executed : 1

download error

: 2

ROM/RAM is discriminated by the status of DBUSY signal after

hardware reset. If RAM, the servo control code is downloaded.

If no error is found, the version No. is read from address:200, and

displayed.

If ROM, the version No. is read from address:200 immediately.

Compare displayed data with existing data.

If RAM, “DSP Download Rev.=xxxx” is displayed.

If ROM, “DSP Mask ROM Rev.=xxxx” is displayed.

(5-5) Servo DSP Register

(Program download)

→

Data write

→

Read matching check

Error 04: Data read error

05: Write/read data mismatch error

13: DSP data not ready

14: DSP download error

The download flag is checked, and if 0, the program is downloaded.

However, in the case of ROM, it is not downloaded.

Unless download error occurs, the content of address 200h of DSP

(IC506) is read for saving, then checking starts. In this check, 16

kinds of patterns are written to the address 200h by shifting 1 bit

each from 0x0001 toward the left, then they are read.

If write/read mismatch error occurred, checking can be repeated.

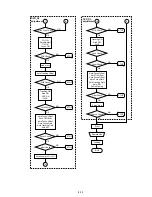

(5-6) Servo DSP Reset Line

Register write

→

Hard reset

→

Register read

Error 02: Reset error

13: DSP data not ready

14: DSP download error

In the case of RAM, this diagnosis checks that the register cannot

be read after hardware reset. Unless download error occurs, the

content of address 200h of DSP (IC506) is read, and after hard-

ware reset, the data is read again for comparison.

The check results in OK, if the register cannot be read, or data are

not matched even if it can be read. The reset error occurs if read

data are same as that before hardware reset.

In the case of ROM, whether the version No. is initialized by the

reset is checked. First, the version No. is read, then its comple-

ment is written.

After hardware reset, the data is read again and if it matches the

written data, the reset error occurs.

(6) Data Source

(6-2) Register in ARP (IC806)

Register write

→

Register read matching check

Error 05: Write/read data mismatch error

Data from “0x00” up to “0xff” are written to 12 registers where all

bits can be written and read, then read to check for matching.

If write/read mismatch error occurred, checking can be repeated.

(6-3) Reset Line in ARP (IC806)

Register write

→

Hard reset

→

Register read

Error 02: Reset error

05: Write/read data mismatch error

After “0xfe” is written to the INTEN3 register, whether it is ini-

tialized to “0x00” by the reset pulse signal is checked.

To make sure, the written data is read to check for matching be-

fore reset is executed.

(6-4) DRAM (IC810) in ARP

ROM data

→

ARP (IC806)

→

DRAM (IC810)

→

ARP (IC806)

read matching check

Error 03: Data write error (ARP (IC806) is not enabled for data

writing)

04: Data read error (ARP (IC806) is not enabled for data

reading)

05: Write/read data mismatch error

ROM (IC803) patterns are copied to all areas to be checked. Each

time 256 bytes are copied, the addresses of copy source (ROM)

are returned by 254 bytes. In detail check, all areas are checked to

verify all bits in DRAM (IC810), then the inverted data are further

checked in the same manner. The bus width of ARP (IC806) is 16

bits. This check program displays addresses in 16 bits.

Overwriting by the shadow can be detected, as the data are written

to all areas, then read. In the detail check, all areas of RAM (IC802)

are checked twice by inverting the data, while in the simple check

one block is checked, then subsequent 4 blocks are skipped, and

also inverted data are not checked.

If write/read mismatch error occurred, checking can be repeated.

(6-5) Interrupt Line in ARP (IC806)

Data transfer request

→

Data transfer stop interruption from ARP

(IC806)

Error 21: ARP (IC806) interruption is not detected

AC-3 audio data stored in ROM (IC803) are transferred to the

ARP (IC806), then the designated sector data output stop inter-

ruption from ARP (IC806) is detected.

To discriminate the Decrypt (IC811) interruption which is also

sent in the same line, the Decrypt (IC811) interruption is all masked.

Summary of Contents for DVP-S500D

Page 12: ...1 2 ...

Page 13: ...1 3 ...

Page 14: ...1 4 ...

Page 15: ...1 5 ...

Page 16: ...1 6 ...

Page 17: ...1 7 ...

Page 18: ...1 8 ...

Page 19: ...1 9 ...

Page 20: ...1 10 ...

Page 21: ...1 11 ...

Page 22: ...1 12 1 12 E ...

Page 52: ...7 5 E 1 2 10 12 14 24 25 CN252 MB 78 BOARD Side B ...