51

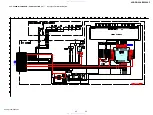

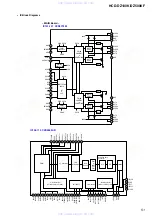

HCD-DZ100K/DZ500KF

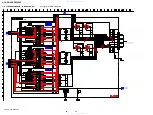

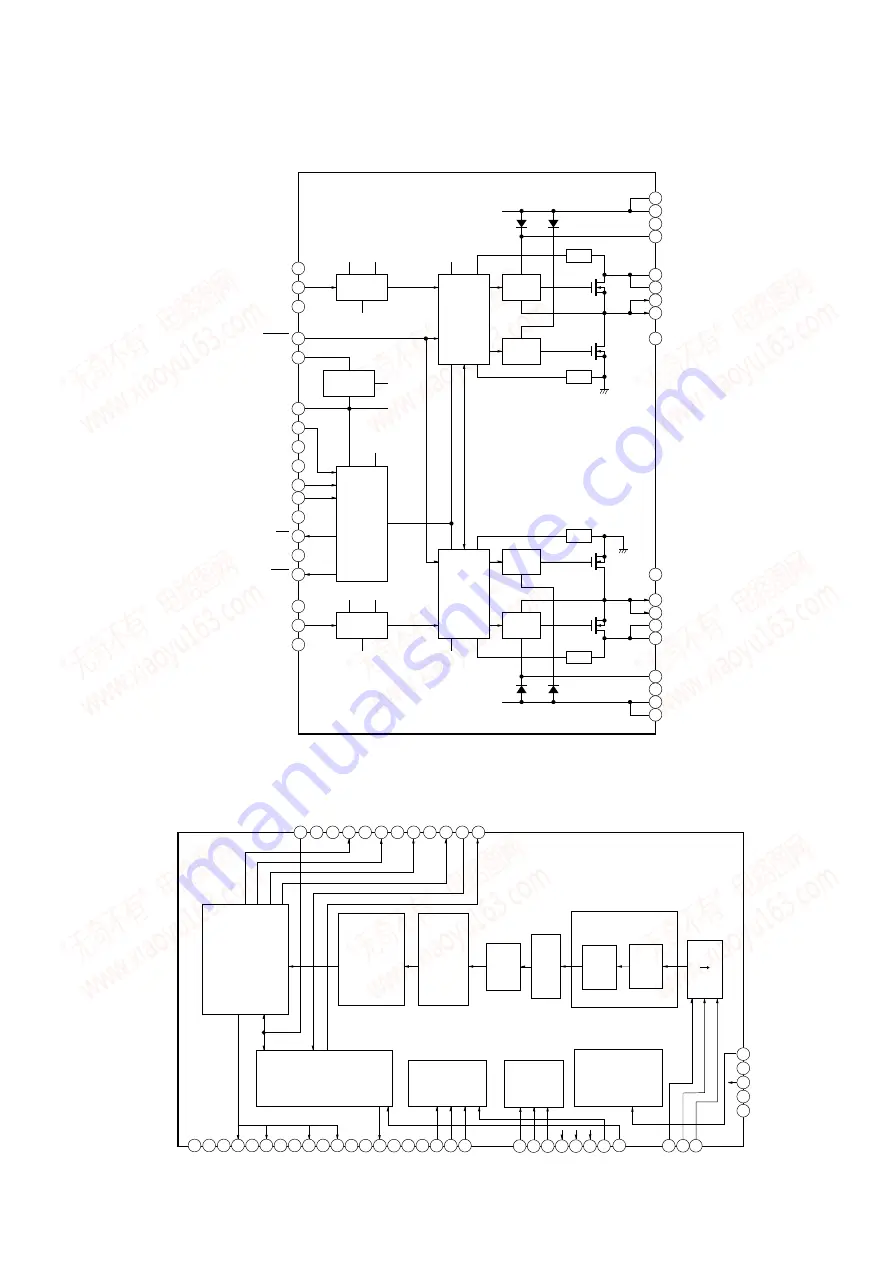

IC108-110 CXD9843AR

IC101-10

7

CXD9774M

– MAIN Board –

RESET 4

GND 1

GND 3

PWM BP 2

DREG RTN 5

GVDD 6

M3 7

M1 10

M2 11

DVDD 12

DREG 8

DGND 9

DGND 14

GND 16

GND 18

PWM

RECEIVER

TIMING

CONTROL

&

PROTECTION

SD 13

OTW 15

DIGITAL

REGULATOR

PROTECTION

LOGIC

OT

&

UVP

DVDD DREG

DREG

DGND

PWM AP 17

PWM

RECEIVER

DVDD DREG

DGND

DREG

GVDD

DREG

GATE

DRIVE

GVDD B

35

GVDD B

36

BST B

33

PVDD B

32

PVDD B

31

OUT B

30

OUT B

29

GND

28

GND

34

GATE

DRIVE

OCH

OCL

TIMING

CONTROL

&

PROTECTION

DREG

GATE

DRIVE

GVDD A

20

GVDD A

19

BST A

22

PVDD A

23

PVDD A

24

OUT A

25

OUT A

26

GND

27

GND

21

GATE

DRIVE

OCH

OCL

GVDD

GVDD

S

P

Sampling Rate

Converter

DF1

DF2

Gain

Control

Filter

&

LOW

CUT

Filter

Serial Control

Liner

Interpolator

∆ ∑

Converter

XVSS

INIT/MUTE

Clock Generator

Clock Generator

(Secondary Clock System)

1

VSUBC

2

VSSR

VSSL

VSSL

VSSR

3

OUTR2

OUTL2

OUTR1

OUTL1

4

VDDR

DVDD

DVSS

VDDL

5

6

7

8

XOVSS

XOVDD

9

XFSOOUT

10 11

NSPMUTE

12

SOFTMUTE

13

PGMUTE

SCSHIFT

14

SCDT

15

SCLA

TCH

OVF FLAGR

OVF FLAGL

16

SFLAG

INIT

17

MCKSEL

18

LRCK

19

BCK

20

D

ATA

BFVDD

BFVSS

TEST

DVDD

XFSIIN

21

42

43

41 40 39 38 37

XFSOIN

36

XVDD

35

HPVDDL

34

HPOUTL2

33

HPVSSL

32

31

HPVDDR

30

HPOUTR1

HPOUTL1

29

28

HPVSSR

27

26

25

HPOUTR2

24

FSOI

23

FSOCKO

22

44

45

46

47

48

(Primary Clock System)

•

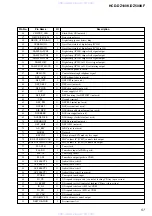

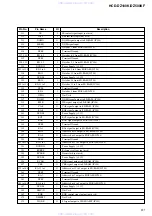

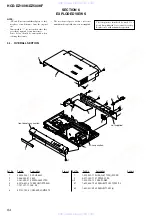

IC Block Diagrams

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299