7-8

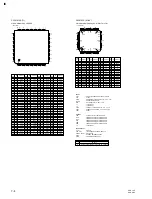

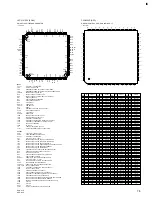

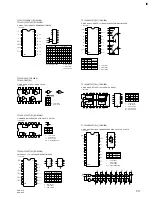

HSR-1/1P

HSR-2/2P

IC

GND

V

DD

V

DD

GND

GND

GND

NC

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

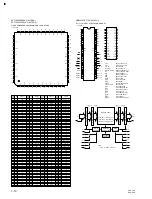

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

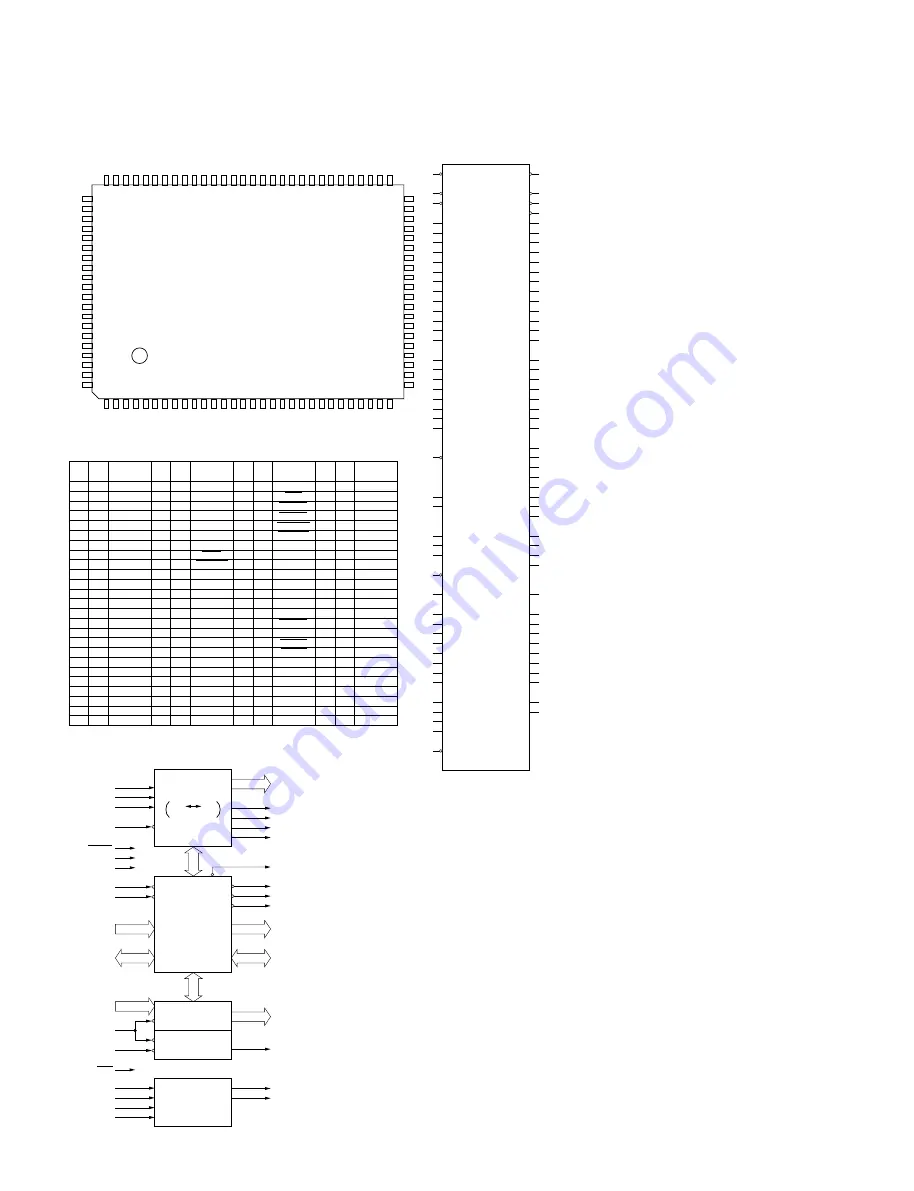

C-MOS 8-MPU COMMUNICATION CONTROLLER WITH PARALLEL PORT

—TOP VIEW—

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

O

I

I

I

I

I

O

I

I

I

I

I

I

I

—

—

I

I

I

I

I

I

I

I

I

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

I

O

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

—

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

—

—

I

I

I

I

I

I

I

I

O

D0 RAM

A12 RAM

A11 RAM

A10 RAM

A9 RAM

A8 RAM

A7 RAM

A6 RAM

A5 RAM

A4 RAM

A3 RAM

A2 RAM

A1 RAM

A0 RAM

GND

V

DD

INP 07

INP 06

INP 05

INP 04

INP 03

INP 02

INP 01

INP 00

OUT 27

A0 CPU

WAIT

CPU WR

CPU RD

MPUIF CS

CONT CS

D7 CPU

D6 CPU

D5 CPU

D4 CPU

D3 CPU

D2 CPU

D1 CPU

D0 CPU

RAM WR

GND

RAM OE

RAMCE

D7 RAM

D6 RAM

D5 RAM

D4 RAM

D3 RAM

D2 RAM

D1 RAM

V SYNC

VSNC LEN

HV CLK

HD

VD

S PULS IN

S PULS OUT

TES 1

P ON RST

SYSTEM CK

CPU CK

A12 CPU

A11 CPU

A10 CPU

GND

V

DD

A9 CPU

A8 CPU

A7 CPU

A6 CPU

A5 CPU

A4 CPU

A3 CPU

A2 CPU

A1 CPU

O

O

O

O

O

O

O

O

I

I

I

O

O

O

—

O

O

O

O

O

O

O

O

—

O

OUT26

OUT25

OUT24

OUT23

OUT22

OUT21

OUT20

INT

H SNC

S RDY

S RESP

SCK

SCMD

STRB

GND

MPUCS7

MPUCS6

MPUCS5

MPUCS4

MPUCS3

MPUCS2

MPUCS1

MPUCS0

N.C

H SYNC

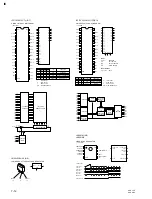

PIN

NO.

PIN

NO.

PIN

NO.

PIN

NO.

I/O

SIGNAL

I/O

I/O

I/O

SIGNAL

SIGNAL

SIGNAL

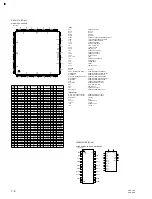

INPUT

A0CPU - A12CPU

CONT CS

CPU CK

CPU RD

CPU WR

HD

H SNC

HV CLK

INP 00 - 07

MPUIF CS

P ON RST

S PULS

S RDY

S RESP

SYSTEM CK

TES 1

VD

VSNC LEN

OUTPUT

A0RAM - A12RAM

H SYNC

INT

MPUCS0 - MPUCS7

OUT 20 - 27

RAM CE

RAM OE

RAM WR

SCK

SCMD

S PULS

STRB

V SYNC

WAIT

INPUT/OUTPUT

D0CPU - D7CPU

D0RAM - D7RAM

; CPU ADDRESS BUS

; INTERNAL/PARALLEL PORT

; CPU CLOCK

; CPU READ STROBE

; CPU WRITE STROBE

; VIDEO HORIZONTAL SYNCHRONIZING PULSE

; SERIAL RECEIVE WAIT

; VIDEO VERTICAL SAMPLING PULSE (13.5 MHz)

; PARALLEL PORT

; EXTERNAL RAM CHIP SELECT

; POWER IN RESET (L)

; MEDIOCRITY CLOCK PULSE

; SERIAL TRANSMISSION LEADY

; SERIAL RECEIVE DATA

; SYSTEM CLOCK

; TEST (L)

; VIDEO VERTICAL SYNCHRONIZING PULSE

; VIDEO VERTICAL SYNCHRONIZING PULSE OUTPUT

WIDTH CONTROL

; EXTERNAL RAM ADDRESS BUS

; VIDEO HORIZONTAL SYNCHRONIZING PULSE

; SERIAL RECEIVE END

; SERIAL CORRESPONDENCE ENABLE

; PARALLEL PORT

; EXTERNAL RAM CHIP SELECT

; EXTERNAL RAM OUTPUT ENABLE

; EXTERNAL RAM WRITE STROBE

; SERIAL CORRESPONDENCE CLOCK

; SERIAL TRANSMISSION DATA

; MEDIOCRITY CLOCK PULSE FREQUENCY (1/2-1/27)

; SERIAL TRANSMISSION STROBE

; VIDEO VERTICAL SYNCHRONIZING PULSE

; CPU WAIT

; CPU DATA BUS

; EXTERNAL RAM DATA BUS

55

54

53

51

50

49

48

47

46

45

44

43

42

39

38

37

64

63

62

61

60

59

58

57

34

35

36

9

10

11

56

31

99

98

97

96

95

94

93

92

30

29

28

27

33

52

65

67

68

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

23

22

21

20

19

18

17

16

8

12

13

14

32

7

6

5

4

3

2

1

100

25

26

MPUIF CS

CPU RD

CPU WR

A0CPU

A1CPU

A2CPU

A3CPU

A4CPU

A5CPU

A6CPU

A7CPU

A8CPU

A9CPU

A10CPU

A11CPU

A12CPU

D0CPU

D1CPU

D2CPU

D3CPU

D4CPU

D5CPU

D6CPU

D7CPU

P ON RST

SYSTEM CK

CPU CK

H SNC

S RDY

S RESP

CONT CS

S PULS IN

INP 00

INP 01

INP 02

INP 03

INP 04

INP 05

INP 06

INP 07

VD

HD

HV CLK

VSNC LEN

TES 1

WAIT

RAM WR

RAM OE

RAM CE

A0RAM

A1RAM

A2RAM

A3RAM

A4RAM

A5RAM

A6RAM

A7RAM

A8RAM

A9RAM

A10RAM

A11RAM

A12RAM

D0RAM

D1RAM

D2RAM

D3RAM

D4RAM

D5RAM

D6RAM

D7RAM

MPUCS0

MPUCS1

MPUCS2

MPUCS3

MPUCS4

MPUCS5

MPUCS6

MPUCS7

INT

SCK

SCMD

STRB

S PULS OUT

OUT 20

OUT 21

OUT 22

OUT 23

OUT 24

OUT 25

OUT 26

OUT 27

H SYNC

V SYNC

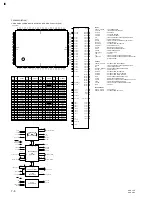

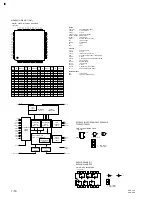

TRANSMITTER

P S

CONVERTER

DATA/ADDRESS

BUS

CONTROL

PARALLEL PORT

CLOCK

PRESCALER

SYNC

GENERATOR

9

10

11

55

H SNC

S RDY

S RESP

MPUIF CS

P ON PST

SYSTEM CK

CPU CK

CPU WR

CPU RD

A0CPU - A12CPU

D0CPU - D7CPU

INP 00 - INP 07

CONT CS

S PULS IN

TES 1

HD

VD

VSNC LEN

HV CLK

34

35

36

53

54

37 - 39,

42 - 51

57 - 64

92 - 99

56

37

33

29

30

27

28

16 - 23

MPUCS0 - MPUCS7

INT

SCK

SCMD

STRB

WAIT

A0RAM - A12RAM

D0RAM - D7RAM

OUT20 - OUT27

S PULS OUT

H SYNC

V SYNC

RAMWR

RAMOE

RAMCE

8

12

13

14

52

65

67

68

77 - 89

69 - 76

1 - 7, 100

32

25

26

CXD8804Q (SONY)

Summary of Contents for HSRA-11

Page 6: ......

Page 74: ......

Page 84: ...9 10 9 10 HSR 1 1P HSR 2 2P ...

Page 91: ......

Page 98: ......

Page 109: ......

Page 111: ...10 15 10 15 HSR 1 1P HSR 2 2P CM 56 CM 56 CM 56 B SIDE SUFFIX 11 ...

Page 112: ...10 16 10 16 HSR 1 1P HSR 2 2P ...

Page 115: ...10 19 10 19 HSR 1 1P HSR 2 2P JC 19 C JC 19 C JC 19 C B SIDE SUFFIX 21 ...

Page 116: ...10 20 10 20 HSR 1 1P HSR 2 2P RP 228 RP 228 RP 228 A SIDE SUFFIX 11 ...

Page 118: ......

Page 141: ...2 3 4 5 I J K L M N O P 11 13 b1 11 13 b1 HSR 1 1P HSR 2 2P 1 ...

Page 166: ...2 3 4 5 A B C D E F G H 11 32 b 11 32 b HSR 1 1P HSR 2 2P 1 ...

Page 180: ...2 3 4 5 A B C D E F G H 11 32 a 11 32 a HSR 1 1P HSR 2 2P 1 ...

Page 188: ...2 3 4 5 A B C D E F G H 11 40 11 40 HSR 1 1P HSR 2 2P 1 ...

Page 204: ...11 56 11 56 HSR 1 1P HSR 2 2P JC 19 C 8 9 JC 19 C 8 9 ...

Page 221: ...2 3 4 5 I J K L M N O P 11 73 b 11 73 b HSR 1 1P HSR 2 2P 1 ...

Page 226: ......