7-12

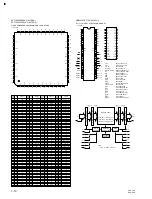

HSR-1/1P

HSR-2/2P

IC

1

0

x

HI-Z

: HIGH LEVEL

: LOW LEVEL

: DON’T CARE

: HIGH IMPEDANCE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

A16

IN

A14

IN

A12

IN

A7

IN

A6

IN

A5

IN

A4

IN

A3

IN

A2

IN

A1

IN

A0

IN

I/O0

I/O1

I/O2

NC

GND

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

A15

IN

CS2

IN

WE

IN

A13

IN

A8

IN

A9

IN

A11

IN

OE

IN

A10

IN

CS1

IN

I/O7

I/O6

I/O5

I/O4

I/O3

V

DD

12

11

10

9

8

7

6

5

27

26

23

25

4

28

3

31

2

29

24

22

30

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

WE

OE

CS1

CS2

13

14

15

17

18

19

20

21

I/O0

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

CS1

1

x

0

0

0

WE

x

x

1

1

0

CS2

x

0

1

1

1

OE

x

x

1

0

x

I/O

FUNCTION

HI-Z

HI-Z

HI-Z

DATA OUT

DATA IN

INPUTS

STANDBY

STANDBY

OUTPUTS DISABLED

READ DATA

WRITE DATA

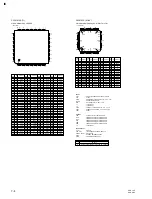

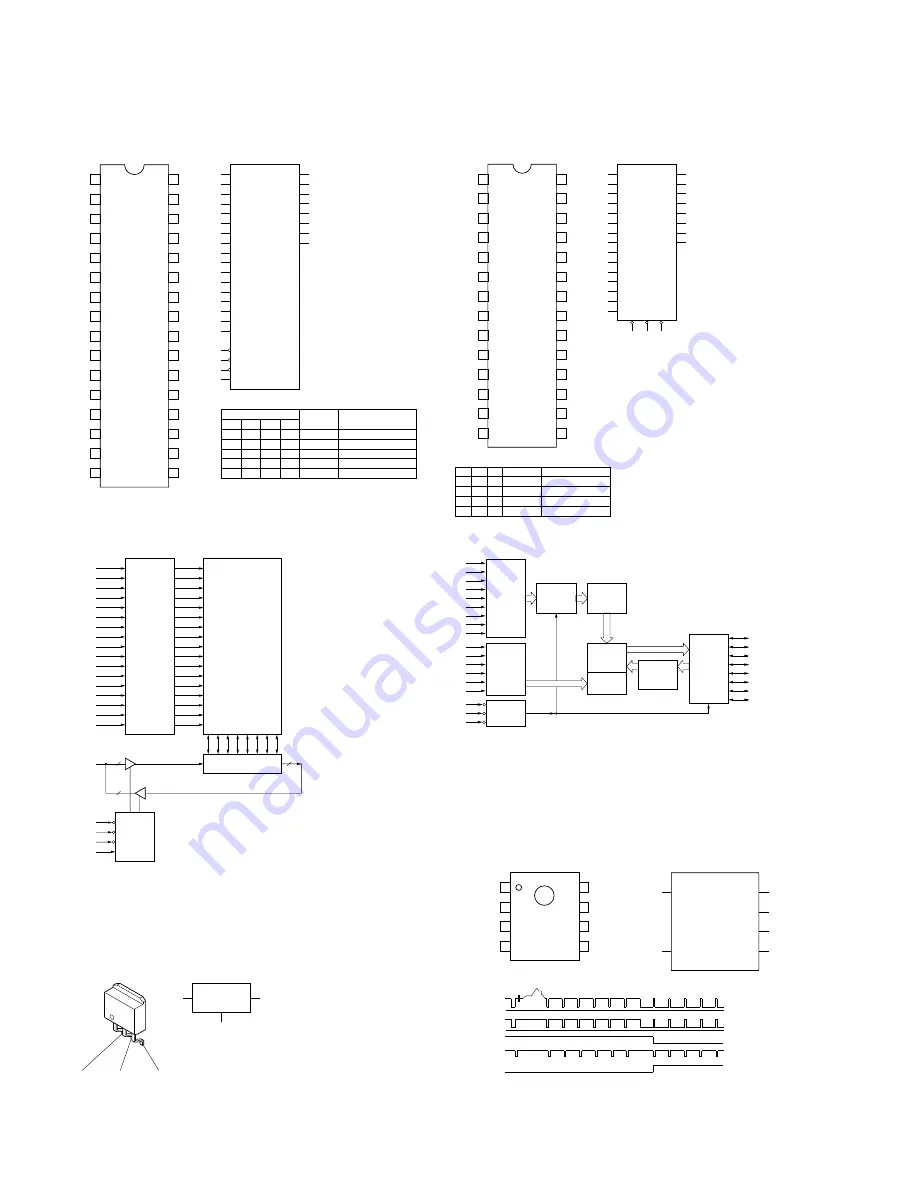

C-MOS 1 M (128

x

8)-BIT SRAM

—TOP VIEW—

ADDRESS

DECODER

1,048,576-BIT

MEMORY ARRAY

I/O CONTROLLER

CONTROL

LOGIC

12

11

10

9

8

7

6

5

27

26

23

25

4

28

3

31

2

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

29

24

22

30

WE

OE

CS1

CS2

13 - 15

17 - 21 8

I/O0 - I/O7

8

8

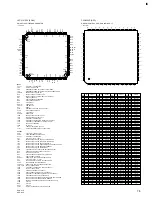

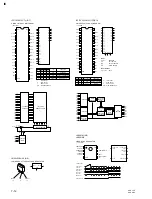

C-MOS 256 K (32 K

x

8)-BIT SRAM

—TOP VIEW—

CS

1

0

0

0

OE

x

1

0

x

FUNCTION

NO SELECTION

OUTPUT DISABLE

READ

WRITE

WE

x

1

1

0

OUTPUTS

HI-Z

HI-Z

D

OUT

D

IN

A14

IN

A12

IN

A7

IN

A6

IN

A5

IN

A4

IN

A3

IN

A2

IN

A1

IN

A0

IN

I/O1

I/O2

I/O3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

V

DD

WE

IN

A13

IN

A8

IN

A9

IN

A11

IN

OE

IN

A10

IN

CS

IN

I/O8

I/O7

I/O6

I/O5

I/O4

GND

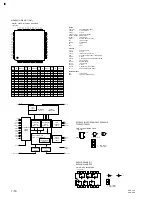

10

9

8

7

6

5

4

3

25

24

21

23

2

26

1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

11

12

13

15

16

17

18

19

WE

27

CS

20

OE

22

INPUT

A0 - A14

CS

OE

WE

INPUT/OUTPUT

I/O1 - 1/O8

: ADDRESS

: CHIP SELECT

: OUTPUT ENABLE

: WRITE ENABLE

: DATA

0

1

x

HI-Z

: LOW LEVEL

: HIGH LEVEL

: DON’T CARE

: HIGH IMPEDANCE

A0

A1

A2

A3

A4

A5

A6

A7

A8

10

9

8

7

6

5

4

3

25

BUFFER

A9

A10

A11

A12

A13

A14

24

21

23

2

26

1

BUFFER

CS

OE

WE

20

22

27

CONTROL

CIRCUIT

ROW

DECODER

512

x

512

MEMORY

ARRAY

COLUMN

I/O

COLUMN

DECODER

INPUT

DATA

CIRCUIT

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

11

12

13

15

16

17

18

19

I/O

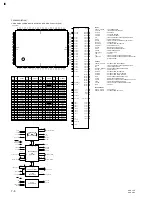

BUFFER

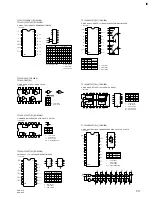

COMPOSITE

SYNC

OUT

COMPOSITE

VIDEO

IN

VERTICAL

SYNC

OUT

ODD/EVEN

OUT

RSET

BURST/BACK

OUT

TIMING CHART

COMPOSITE

VIDEO IN

COMPOSITE

SYNC OUT

VERTICAL

SYNC OUT

BURST OUT

ODD/EVEN OUT

GND

V

CC

COMPOSITE

VIDEO

RSET

COMPOSITE

SYNC

VERTICAL

SYNC

ODD/EVEN

BURST/BACK

1

2

3

4

8

7

6

5

1

3

7

5

2

6

VIDEO SYNC SEPARATOR

—TOP VIEW—

LOW DROPOUT TYPE VOLTAGE REGULATOR

1

INPUT

3

2

OUTPUT

GND

INPUT

(1)

GND

(2)

OUTPUT

(3)

IDT71024S15Y-TL (IDT)

IDT71V256SA15Y (IDT)SOJ

LM1881M (NS)

LM1881MX

LM2940CSX-5.0 (NS)

Summary of Contents for HSRA-11

Page 6: ......

Page 74: ......

Page 84: ...9 10 9 10 HSR 1 1P HSR 2 2P ...

Page 91: ......

Page 98: ......

Page 109: ......

Page 111: ...10 15 10 15 HSR 1 1P HSR 2 2P CM 56 CM 56 CM 56 B SIDE SUFFIX 11 ...

Page 112: ...10 16 10 16 HSR 1 1P HSR 2 2P ...

Page 115: ...10 19 10 19 HSR 1 1P HSR 2 2P JC 19 C JC 19 C JC 19 C B SIDE SUFFIX 21 ...

Page 116: ...10 20 10 20 HSR 1 1P HSR 2 2P RP 228 RP 228 RP 228 A SIDE SUFFIX 11 ...

Page 118: ......

Page 141: ...2 3 4 5 I J K L M N O P 11 13 b1 11 13 b1 HSR 1 1P HSR 2 2P 1 ...

Page 166: ...2 3 4 5 A B C D E F G H 11 32 b 11 32 b HSR 1 1P HSR 2 2P 1 ...

Page 180: ...2 3 4 5 A B C D E F G H 11 32 a 11 32 a HSR 1 1P HSR 2 2P 1 ...

Page 188: ...2 3 4 5 A B C D E F G H 11 40 11 40 HSR 1 1P HSR 2 2P 1 ...

Page 204: ...11 56 11 56 HSR 1 1P HSR 2 2P JC 19 C 8 9 JC 19 C 8 9 ...

Page 221: ...2 3 4 5 I J K L M N O P 11 73 b 11 73 b HSR 1 1P HSR 2 2P 1 ...

Page 226: ......