7-15

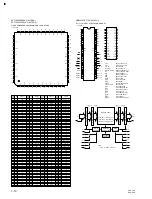

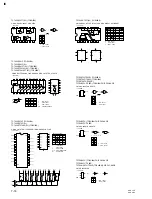

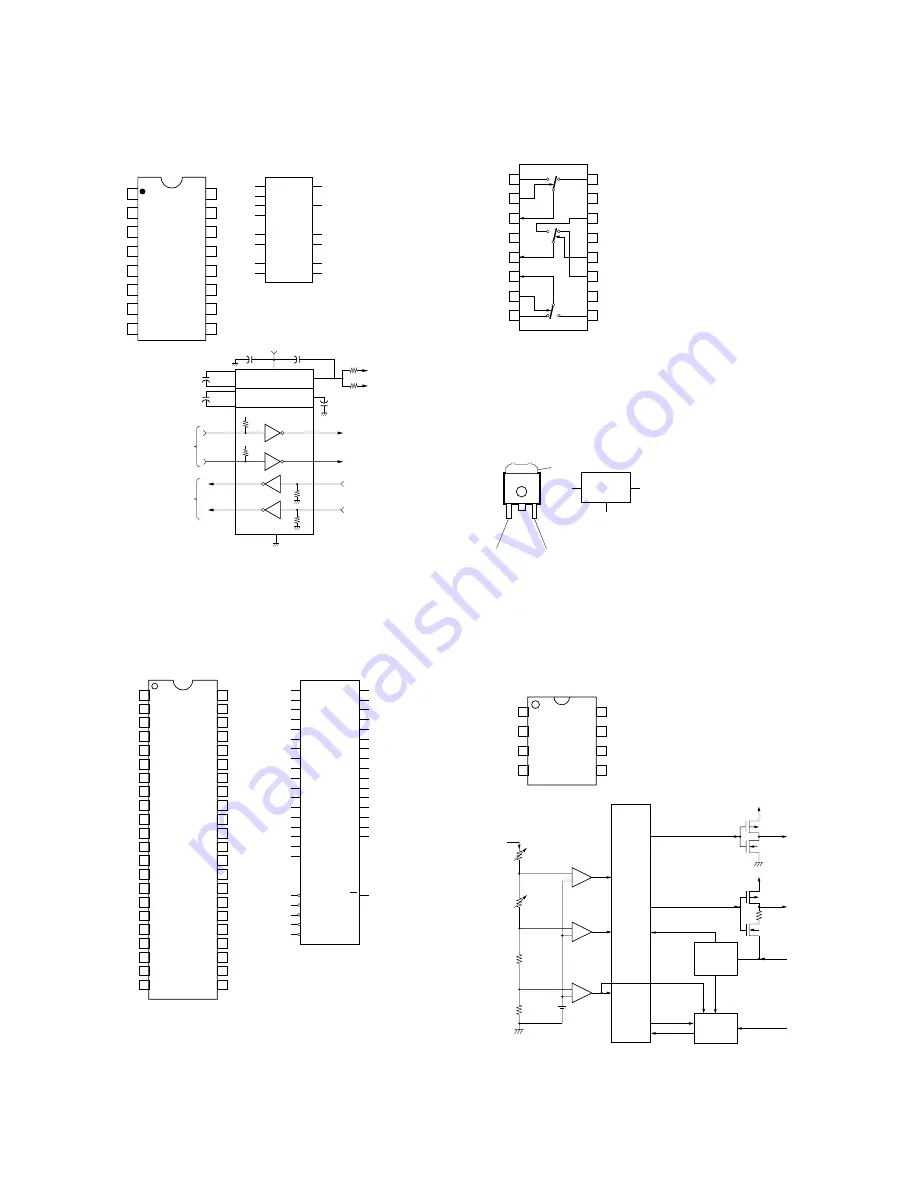

HSR-1/1P

HSR-2/2P

IC

1

16

V

DD

GND

2

15

V

+

C1

+

3

14

C1

_

4

13

C2

+

R1

IN

5

12

C2

_

R1

OUT

T1

OUT

6

11

V

_

T1

IN

7

10

T2

OUT

T2

IN

8

9

R2

IN

R2

OUT

1

C1

+

3

C1

_

4

C2

+

5

C2

_

11

T1

10

T2

13

R1

8

2

6

14

7

12

9

R2

V

+

V

_

T1

T2

R1

R2

R1, 2

T1, 2

; RECEIVER 1, 2

; TRANSMITTER 1, 2

+

5 V

INPUT

16

1

3

+

C1

4

5

11

+

+

C2

T1

–10 V

+

5 V

+

10 V

2

6

14

R

R

DTR

DSR

TXD

RS-232 OUTPUT

400 K

10

T2

+

5 V

7

RTS

RS-232 OUTPUT

400 K

12

R1

13

RXD

RS-232 INPUT

5 K

9

R2

8

CTS

RS-232 INPUT

5 K

15

TTL/CMOS

INPUTS

TTL/CMOS

OUTPUTS

+

5 V TO

+

10 V

VOLTAGE DOUBLER

+

10 V TO

_

10 V

VOLTAGE INVERTER

+

+

C3

C5

C4

ALL CAPACITORS 0.1µF

RS-232 TRANSMITTER/RECEIVER

—TOP VIEW—

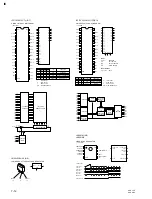

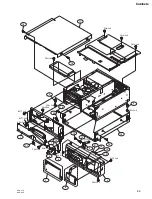

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

NC

GND

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

GND

V

DD

RY/

BY

OUT

A17

IN

A7

IN

A6

IN

A5

IN

A4

IN

A3

IN

A2

IN

A1

IN

A0

IN

CE

IN

OE

IN

DQ0

I/O

DQ8

I/O

DQ1

I/O

DQ9

I/O

DQ2

I/O

DQ10

I/O

DQ3

I/O

DQ11

I/O

RESET

IN

WE

IN

A8

IN

A9

IN

A10

IN

A11

IN

A12

IN

A13

IN

A14

IN

A15

IN

A16

IN

BYTE

IN

DQ15/A-1

I/O

DQ7

I/O

DQ14

I/O

DQ6

I/O

DQ13

I/O

DQ5

I/O

DQ12

I/O

DQ4

I/O

3

34

35

36

37

38

39

40

41

42

4

5

6

7

8

9

10

11

43

33

44

12

14

DQ15/A-1

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

RY/BY

31

29

27

25

22

20

18

16

30

28

26

24

21

19

17

15

2

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

WE

BYTE

RESET

CE

OE

INPUT

A0 - A17, A - 1

BYTE

CE

OE

RESET

WE

: ADDRESS

: 8-BIT, 16-BIT MODE SELECT

: CHIP ENABLE

: OUTPUT ENABLE

: HARDWARE RESET

: WRITE ENABLE

OUTPUT

RY/

BY

INPUT/OUTPUT

DQ0 - DQ15

: READY/BUSY

: DATA

C-MOS 4 M (262,144

x

16)-BIT FLASH MEMORY

—TOP VIEW—

MAX232CWE (MAXIM)

MAX232CWE-TE-2

MBM29F400BC-70PFTN (FUJITSU)

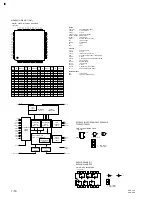

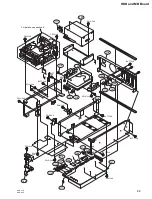

IN1B

CTL1

OUT1

OUT2

OUT3

CTL3

IN3A

1

2

3

4

5

6

7

8

H

L

H

L

L

H

16

15

14

13

12

11

10

9

GND1

V

CC

GND3

IN1A

IN2B

CTL2

IN2A

IN3B

GND2

3-CIRCUIT 2-INPUT SIGNAL SWITCH

—TOP VIEW—

IN

(3)

OUT

(1)

3

1

2

IN

OUT

GND

POSITIVE VOLTAGE REGULATOR

—FRONT VIEW—

GND

(2)

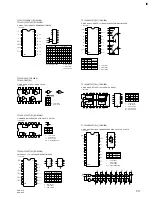

1

2

3

4

8

7

6

5

SENS

IN

DO

OUT

CO

OUT

VM

IN

V

CC

NC

ICT

IN

V

EE

BATTERY PROTECTOR

—TOP VIEW—

INPUTS

ICT

SENS

VM

OUTPUTS

CO

DO

: SENSE DELAY CAPACITOR

: EXCESSIVE CHARGE/DISCHARGE SENSE

: OVER CURRENT SENSE

: CHARGE CONTROL

: DISCHARGE CONTROL

CONTROL

LOGIC

+

_

+

_

+

_

2

DO

3

CO

R COL

OVER

CURRENT

DETECTOR

DELAY

DELAY

INHIBIT

OVER CURRENT

DELAY STARTER

EXCESSIVE

CHARGING/

DISCHARGING

DELAY

STARTER

CONTROL

FINAL

EXCESSIVE

CHARGING

DETECTION

COMPARATOR

REFERENCE

VOLTAGE

4

VM

6

ICT

1

SENS

EXCESSIVE

CHARGING

DETECTION

COMPARATOR

EXCESSIVE

DISCHARGING

DETECTION

COMPARATOR

NJM2286M-T1 (JRC)

NJM78M12DLA(TE1) (JRC)+12 V(500 mA)

S-8231AOFN-CAO-T2 (SEIKO I&E)

Summary of Contents for HSRA-11

Page 6: ......

Page 74: ......

Page 84: ...9 10 9 10 HSR 1 1P HSR 2 2P ...

Page 91: ......

Page 98: ......

Page 109: ......

Page 111: ...10 15 10 15 HSR 1 1P HSR 2 2P CM 56 CM 56 CM 56 B SIDE SUFFIX 11 ...

Page 112: ...10 16 10 16 HSR 1 1P HSR 2 2P ...

Page 115: ...10 19 10 19 HSR 1 1P HSR 2 2P JC 19 C JC 19 C JC 19 C B SIDE SUFFIX 21 ...

Page 116: ...10 20 10 20 HSR 1 1P HSR 2 2P RP 228 RP 228 RP 228 A SIDE SUFFIX 11 ...

Page 118: ......

Page 141: ...2 3 4 5 I J K L M N O P 11 13 b1 11 13 b1 HSR 1 1P HSR 2 2P 1 ...

Page 166: ...2 3 4 5 A B C D E F G H 11 32 b 11 32 b HSR 1 1P HSR 2 2P 1 ...

Page 180: ...2 3 4 5 A B C D E F G H 11 32 a 11 32 a HSR 1 1P HSR 2 2P 1 ...

Page 188: ...2 3 4 5 A B C D E F G H 11 40 11 40 HSR 1 1P HSR 2 2P 1 ...

Page 204: ...11 56 11 56 HSR 1 1P HSR 2 2P JC 19 C 8 9 JC 19 C 8 9 ...

Page 221: ...2 3 4 5 I J K L M N O P 11 73 b 11 73 b HSR 1 1P HSR 2 2P 1 ...

Page 226: ......