7-16

HSR-1/1P

HSR-2/2P

IC

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

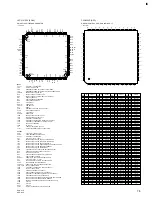

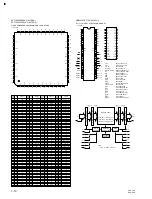

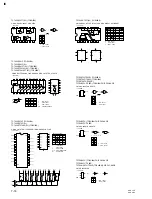

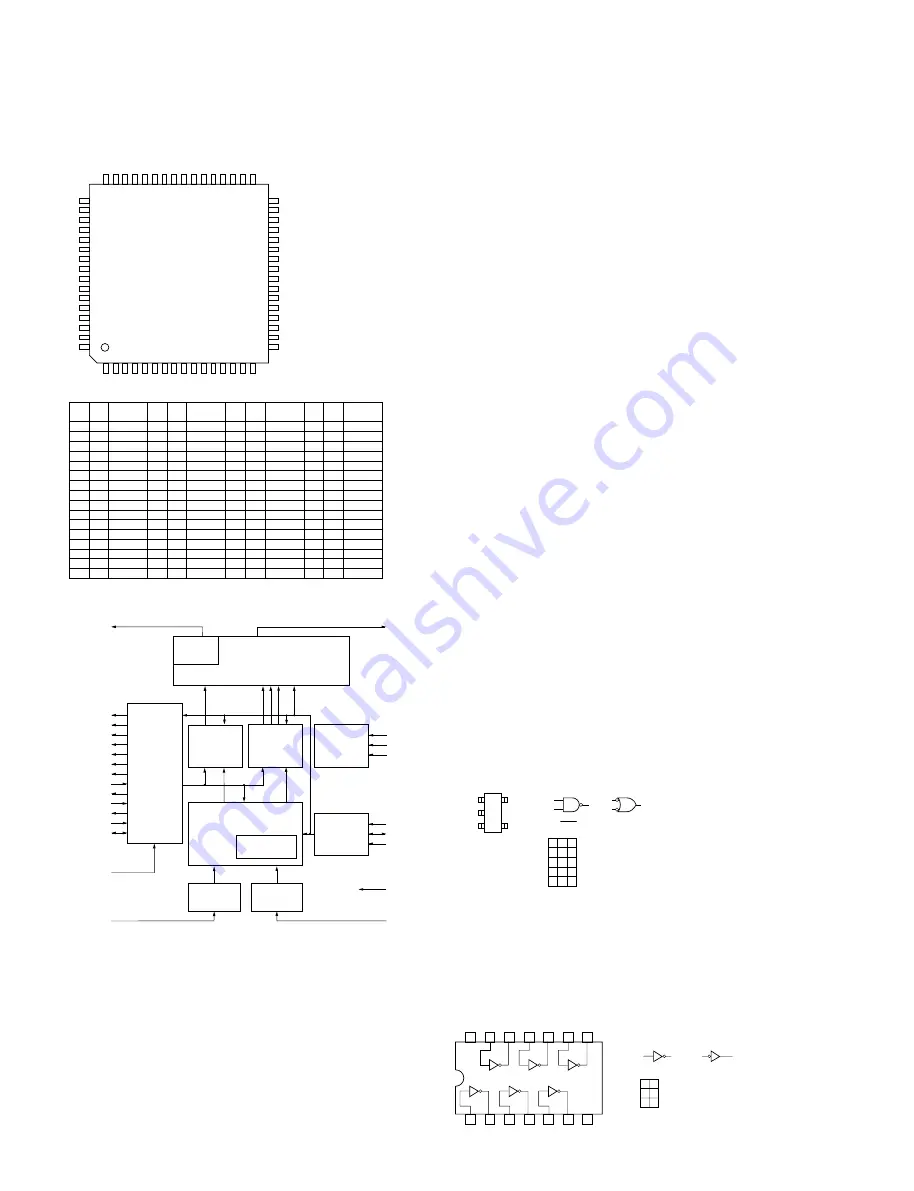

DIGITAL VIDEO NTSC/PAL DECODER

—TOP VIEW—

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

CD0

CD1

CD2

CD3

CD4

CD5

CD6

CD7

CVBS0

CVBS1

CVBS2

CVBS3

CVBS4

CVBS5

CVBS6

CVBS7

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

—

—

I

I/O

I

I

I

I

I

I

I

I

I

I

—

—

V

CC

GND

SCL

SDA

MODE0

MODE1

MODE2

MODE3

RESET L

PLLSEL

CLKSEL

TEST1

SLEEP

TE

GND

V

CC

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

C7

C6

C5

C4

C3

C2

C1

C0

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

—

—

O

O

O

O

O

O

O

O

O

I/O

O

I

—

—

V

CC

GND

ODD

VVALID

HVALID

VSYNC L

HSYNC L

CLKXO

SYSSEL

CLKX2O

VCO CP

SYNC

HSY

CLKX2

GND

V

CC

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

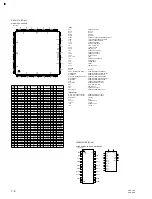

INPUTS

CD0 - CD7

CLKSEL

CLKX2

CVBS0 - CVBS7

MODE0 - MODE3

PLLSEL

RESET L

SCL

SLEEP

TE

TEST1

OUTPUTS

C0 - C7

CLKX2O

CLKXO

HSY

HSYNC L

HVALID

ODD

SYSSEL

VCO CP

VSYNC L

VVALID

Y0 - Y7

INPUTS/OUTPUTS

SDA

SYNC

: CHROMINANCE SIGNAL

: CLOCK SELECT

: CLOCK

: COMPOSITE SIGNAL

: MODE SELECT

: (NOT IN USE)

: SYSTEM RESET (ACTIVE L)

: I

2

C BUS CLOCK

: SLEEP MODE

: TEST

: TEST

: CHROMA SIGNAL

: CLOCK

: INTERNAL CLOCK PULSE

: A/D CONVERTER CLAMP TIMING SIGNAL

: H SYNC

: H EFFECTIVE PICTURE ELEMENT TIMING

: FIELD DISPLAY

: SYSTEM SELECT

: (NOT IN USE)

: V SYNC

: V EFFECTIVE LINES TIMING

: COLOR DIFFERENCE SIGNAL

: I

2

C BUS DATA

: COMPOSITE SYNC SIGNAL

51

ODD

52

VVALID

53

HVALID

8-BIT

(YCbCr)

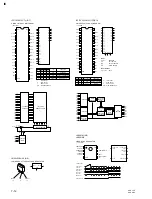

EPILOGUE

BLOCK

OUTPUT

FORMATTER

SYNCHRONI-

ZATION

BLOCK

LUMINANCE

BLOCK

(AGC

+

LPF)

CHROMINANCE

BLOCK

(ACC

+

LPF)

TEST

CONTROL

LOGIC

I

2

C-BUC

CONTROL

LOGIC

PROLOGUE BLOCK

(2Dim. Y/C SEPARATE)

LINE MEMORY

(1Kb)

x

2

DECIMATION

FILTER

DECIMATION

FILTER

54

VSYNC L

55

HSYNC L

61

HSY

57

SYSSEL

27

CLKSEL

56

CLKXO

62

CLKX2

58

CLKX2O

26

PLLSEL

60

SYNC

30

TE

28

TEST1

29

SLEEP

Lum.

chr.

25

RESET L

20

SDA

19

SCL

33 - 40

Y7 - Y0

41 - 48

C7 - C0

59

VCO CP

9 - 16

CVBS7 - CVBS0

21 - 24 MODE3 -

MODE0

1 - 8

CD7 - CD0

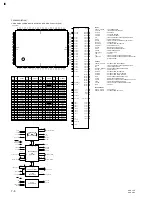

MSM7661GS-BK-R1 (OKI)

1

2

GND 3

A

B

Y

A

B

Y

=

Y = A • B =

A

+

B

A

0

0

1

1

B

0

1

0

1

Y

1

1

1

0

0

1

: LOW LEVEL

: HIGH LEVEL

5 V

DD

4

2

1

4

C-MOS 2-INPUT NAND GATE

—TOP VIEW—

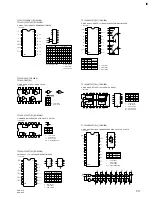

A

A

Y =

Y

14

13

V

DD

GND

12

11

10

9

8

7

6

5

4

3

2

1

A

0

1

Y

1

0

0 : LOW LEVEL

1 : HIGH LEVEL

Y =

A

C-MOS HEX INVERTERS

—TOP VIEW—

SC7S00F (MOTOROLA)CHIP PACKAGE

TC7S00F(TE85R)

SN74HC04ANS (TI)

SN74HC04ANS-E05

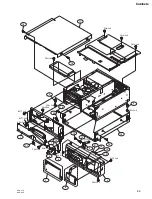

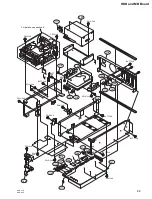

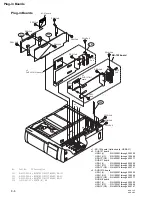

Summary of Contents for HSRA-11

Page 6: ......

Page 74: ......

Page 84: ...9 10 9 10 HSR 1 1P HSR 2 2P ...

Page 91: ......

Page 98: ......

Page 109: ......

Page 111: ...10 15 10 15 HSR 1 1P HSR 2 2P CM 56 CM 56 CM 56 B SIDE SUFFIX 11 ...

Page 112: ...10 16 10 16 HSR 1 1P HSR 2 2P ...

Page 115: ...10 19 10 19 HSR 1 1P HSR 2 2P JC 19 C JC 19 C JC 19 C B SIDE SUFFIX 21 ...

Page 116: ...10 20 10 20 HSR 1 1P HSR 2 2P RP 228 RP 228 RP 228 A SIDE SUFFIX 11 ...

Page 118: ......

Page 141: ...2 3 4 5 I J K L M N O P 11 13 b1 11 13 b1 HSR 1 1P HSR 2 2P 1 ...

Page 166: ...2 3 4 5 A B C D E F G H 11 32 b 11 32 b HSR 1 1P HSR 2 2P 1 ...

Page 180: ...2 3 4 5 A B C D E F G H 11 32 a 11 32 a HSR 1 1P HSR 2 2P 1 ...

Page 188: ...2 3 4 5 A B C D E F G H 11 40 11 40 HSR 1 1P HSR 2 2P 1 ...

Page 204: ...11 56 11 56 HSR 1 1P HSR 2 2P JC 19 C 8 9 JC 19 C 8 9 ...

Page 221: ...2 3 4 5 I J K L M N O P 11 73 b 11 73 b HSR 1 1P HSR 2 2P 1 ...

Page 226: ......