3-9

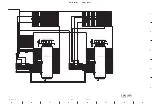

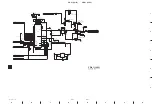

HXC-100/V2 (J, E)

3-9

2

3

4

5

1

A B

C

D

E

F

G

H

CD-61 (5/12)

CD-61 (5/12)

10uF

C500

22

RB520

12

34

56

78

22

RB523

12

34

56

78

0.1uF

C505

FB501

0.1uF

C507

GND

GND

22

RB502

1

2

3

4

5

6

7

8

GND

22

RB517

12

34

56

78

22

RB524

12

34

56

78

22

RB506

1

2

3

4

5

6

7

8

22

R501

GND

0.1uF

C515

22

RB510

12

34

56

78

GND

22

RB503

1

2

3

4

5

6

7

8

22

RB505

1

2

3

4

5

6

7

8

22

RB511

12

34

56

78

1uF

C517

0.1uF

C501

1uF

C508

22

RB521

12

34

56

78

0.1uF

C512

FB500

GND

22

RB504

1

2

3

4

5

6

7

8

GND

0.1uF

C513

22

RB508

12

34

56

78

0.1uF

C510

22

RB509

12

34

56

78

22

RB519

12

34

56

78

0.1uF

C503

FB502

0.1uF

C502

22

RB507

12

34

56

78

22

RB514

12

34

56

78

0.1uF

C506

0.1uF

C516

FB503

22

RB512

12

34

56

78

+1.8V-5

22

RB518

12

34

56

78

22

RB522

12

34

56

78

10uF

C509

GND

22

R500

0.1uF

C514

DAYTONA-MAIN-DDR

004

0.1uF

C511

0.1uF

C504

22

RB513

12

34

56

78

+1.8V-5

22

R509

22

R502

22

R503

22

R510

22

R511

22

R512

22

R513

22

R514

22

R522

22

R521

22

R519

22

R518

22

R516

22

R520

22

R515

22

R517

MT46H16M32LFCM-6IT:B

IC500

DQ16

A8

VDDQ3

C9

DQ17

B7

DQ18

B8

VSSQ3

C1

DQ19

C7

DQ20

C8

VDDQ4

D1

DQ21

D7

DQ22

D8

VSSQ4

D9

DQ23

E7

VDDQ5

E9

DQS1

L2

VDDQ1

A7

DM1

K2

WE

G7

CAS

G8

RAS

G9

CS

H7

BA0

H8

BA1

H9

A10

J7

A0

J8

A1

J9

A2

K7

A3

K9

VDDQ2

B1

VSSQ2

B9

DQ31

A2

VSSQ7

M9

DQ30

B3

DQ29

B2

VDDQ7

M1

DQ28

C3

DQ27

C2

VSSQ6

L1

DQ26

D3

DQ25

D2

VDDQ6

L9

DQ24

E3

VSSQ5

E1

DQS3

E2

VSSQ1

A3

DM2

F8

CK

G3

CK

G2

CKE

G1

A11

H2

A9

H1

A8

J3

A7

J2

A6

J1

A5

K3

A4

K1

A12

H3

VDD1

A9

VDD2

F1

VDD3

R9

VDDQ8

N9

VDDQ9

P1

VDDQ10

R7

VSS1

A1

VSS2

F9

VSS3

R1

VSSQ8

N1

VSSQ9

P9

VSSQ10

R3

DM3

F2

DQS2

E8

DQS0

L8

DQ14

P3

DQ15

R2

DQ9

M2

DQ8

L3

DQ12

N3

DQ11

N2

DQ10

M3

DQ13

P2

DQ6

M8

DQ7

L7

DQ1

P7

DQ0

R8

DQ4

N8

DQ3

N7

DQ2

P8

DQ5

M7

DM0

K8

NC1

F3

NC2

F7

MT46H16M32LFCM-6IT:B

IC501

DQ16

A8

VDDQ3

C9

DQ17

B7

DQ18

B8

VSSQ3

C1

DQ19

C7

DQ20

C8

VDDQ4

D1

DQ21

D7

DQ22

D8

VSSQ4

D9

DQ23

E7

VDDQ5

E9

DQS1

L2

VDDQ1

A7

DM1

K2

WE

G7

CAS

G8

RAS

G9

CS

H7

BA0

H8

BA1

H9

A10

J7

A0

J8

A1

J9

A2

K7

A3

K9

VDDQ2

B1

VSSQ2

B9

DQ31

A2

VSSQ7

M9

DQ30

B3

DQ29

B2

VDDQ7

M1

DQ28

C3

DQ27

C2

VSSQ6

L1

DQ26

D3

DQ25

D2

VDDQ6

L9

DQ24

E3

VSSQ5

E1

DQS3

E2

VSSQ1

A3

DM2

F8

CK

G3

CK

G2

CKE

G1

A11

H2

A9

H1

A8

J3

A7

J2

A6

J1

A5

K3

A4

K1

A12

H3

VDD1

A9

VDD2

F1

VDD3

R9

VDDQ8

N9

VDDQ9

P1

VDDQ10

R7

VSS1

A1

VSS2

F9

VSS3

R1

VSSQ8

N1

VSSQ9

P9

VSSQ10

R3

DM3

F2

DQS2

E8

DQS0

L8

DQ14

P3

DQ15

R2

DQ9

M2

DQ8

L3

DQ12

N3

DQ11

N2

DQ10

M3

DQ13

P2

DQ6

M8

DQ7

L7

DQ1

P7

DQ0

R8

DQ4

N8

DQ3

N7

DQ2

P8

DQ5

M7

DM0

K8

NC1

F3

NC2

F7

M0_DQ[18]

MEM_CKE

M1_DQ[22]

ADDR[6]

DDR_1_D[11]

DDR_MEM_CS

M0_DQ[29]

DDR_A[11]

DDR_0_D[14]

M0_DQ[3]

DDR_0_D[6]

DDR_A[8]

DDR_MEM_WE

M0_DQ[18]

ADDR[3]

MEM_CKE

DDR_A[11]

DDR_A[7]

M1_DQ[16]

DDR_0_D[20]

M1_DQS[0]

DDR_1_D[7]

DDR_BA0

DDR_BA1

DDR_0_D[10]

M1_DQ[7]

M1_DQ[17]

M1_DQ[3]

M0_DQ[24]

DDR_A[4]

DDR_0_D[29]

M1_DQ[0]

DDR_A[3]

M1_DQ[17]

DDR_1_D[5]

ADDR[5]

DDR_RAS

DDR_A[12]

DDR_1_DM[3]

M1_DQ[28]

M1_DQ[8]

DDR_0_D[13]

DDR_A[11]

ADDR[8]

M1_DQ[26]

DDR_A[10]

M0_DQ[15]

M1_DQ[6]

DDR_A[12]

M1_DQ[10]

M1_DQ[4]

M0_DQ[2]

M1_DQ[20]

DDR_1_D[19]

DDR_0_D[3]

DDR_MEM_CAS

M1_DQ[19]

M1_DQ[21]

ADDR[1]

DDR_0_D[1]

M0_DQ[28]

M0_DQ[11]

DDR_0_D[11]

M1_DQ[25]

DDR_A[7]

ADDR[2]

M0_DQ[22]

M0_DQ[10]

M0_DQ[25]

DDR_A[9]

M0_DQ[19]

DDR_0_D[22]

M0_DM[1]

M0_DQ[21]

DDR_1_D[24]

M1_DQ[11]

DDR_CKE

DDR_1_D[15]

M0_DQ[7]

M1_DQS[0]

DDR_1_D[26]

M0_DQ[21]

DDR_0_D[26]

M1_DQ[19]

DDR_A[10]

DDR_0_D[30]

MEM_CKE

DDR_A[6]

DDR_0_DQS[3]

M1_DQS[1]

DDR_A[4]

M1_DQ[31]

DDR_A[12]

DDR_BA0

M0_DQ[14]

DDR_0_DQS[2]

M0_DQ[28]

M0_DQ[0]

DDR_0_D[27]

DDR_1_DM[1]

M1_DQ[2]

DDR_0_D[28]

M0_DQ[12]

DDR_A[5]

M1_DQ[9]

M0_DQ[3]

DDR_1_DQS[3]

DDR_A[4]

DDR_1_D[22]

M0_DQ[30]

M0_DQS[0]

M1_DQ[24]

DDR_1_D[14]

DDR_1_D[3]

M1_DQ[25]

DDR_0_D[9]

M0_DQ[13]

DDR_MEM_RAS

M0_DQ[30]

ADDR[12]

M1_DM[3]

M1_DQ[28]

DDR_1_D[6]

EDDR_BA1

M0_DQ[25]

M0_DQ[6]

ADDR[11]

DDR_A[5]

M1_DQ[23]

DDR_0_DM[3]

DDR_A[0]

DDR_CLK

DDR_A[7]

M1_DQ[15]

DDR_A[6]

M1_DQ[31]

DDR_0_D[31]

M0_DQ[1]

M0_DQ[2]

M0_DQ[14]

M0_DQ[1]

M0_DQ[27]

DDR_A[0]

DDR_1_D[25]

M1_DQ[18]

DDR_A[8]

ADDR[10]

DDR_0_D[8]

M0_DQ[26]

M1_DQ[9]

DDR_MEM_WE

M1_DQ[27]

M0_DQ[9]

DDR_1_D[23]

DDR_MEM_RAS

DDR_A[1]

M1_DQ[30]

M0_DQ[20]

M1_DM[3]

M0_DQ[5]

DDR_A[0]

M0_DM[2]

DDR_BA1

M0_DQ[11]

DDR_1_D[18]

M0_DQ[8]

M0_DQS[3]

DDR_A[8]

M0_DQ[31]

DDR_A[1]

M0_DQ[5]

DDR_1_D[4]

DDR_A[2]

DDR_1_D[13]

M0_DQS[2]

DDR_CS

M1_DQ[13]

M1_DQ[14]

M1_DQ[16]

M1_DQ[24]

DDR_1_D[30]

M0_DQ[24]

M1_DQS[2]

DDR_0_DM[1]

M0_DQ[29]

M0_DQ[12]

M1_DM[2]

DDR_A[2]

M1_DQ[29]

M1_DQ[3]

DDR_0_D[7]

DDR_1_DQS[2]

M0_DQ[17]

M1_DQ[6]

DDR_0_D[5]

M0_DQ[20]

M1_DQ[29]

M0_DQ[31]

DDR_0_D[18]

DDR_WE

DDR_1_D[31]

M1_DM[1]

M1_DM[1]

DDR_A[5]

DDR_MEM_CAS

M1_DQ[30]

M0_DM[3]

M0_DQ[4]

DDR_0_D[25]

M1_DQ[2]

M0_DQ[8]

M1_DQ[12]

DDR_0_D[19]

DDR_1_DQS[1]

M0_DQS[1]

M1_DQ[1]

DDR_0_D[15]

M1_DQ[1]

M0_DQ[7]

M0_DQ[13]

M1_DQ[14]

DDR_0_DQS[1]

DDR_1_D[28]

M0_DQ[26]

DDR_0_DQS[0]

DDR_A[9]

M0_DM[3]

DDR_BA1

DDR_CLK

DDR_0_D[24]

DDR_A[3]

DDR_A[2]

M0_DQS[0]

DDR_0_D[2]

DDR_CAS

DDR_A[10]

M1_DQ[21]

DDR_1_D[10]

M0_DQ[4]

DDR_A[1]

DDR_1_D[0]

DDR_A[9]

M0_DM[1]

DDR_1_D[21]

M0_DQ[27]

DDR_0_D[23]

M1_DQ[27]

DDR_BA0

M0_DQ[9]

DDR_A[6]

M1_DQS[3]

ADDR[9]

DDR_0_D[16]

DDR_MEM_RAS

DDR_0_D[17]

DDR_0_D[12]

ADDR[4]

M1_DM[0]

M0_DQ[23]

M1_DQ[13]

DDR_1_D[20]

ADDR[0]

M0_DQ[16]

DDR_MEM_CS

M1_DQ[7]

M1_DQ[11]

M0_DQ[23]

EDDR_BA0

M1_DQ[20]

M1_DQS[2]

M0_DM[0]

M1_DQ[18]

DDR_0_D[4]

DDR_1_D[2]

DDR_1_DQS[0]

M0_DQS[1]

M0_DQ[10]

M1_DQ[10]

DDR_1_D[17]

M0_DQ[6]

M0_DM[0]

M1_DQ[26]

M1_DQS[3]

M1_DQ[4]

DDR_1_D[29]

DDR_1_D[16]

M1_DQ[22]

ADDR[7]

M0_DQ[17]

M0_DQS[2]

DDR_MEM_CS

M1_DQ[5]

M1_DQ[15]

DDR_1_D[1]

M1_DQS[1]

DDR_0_DM[0]

DDR_1_D[9]

DDR_A[3]

M0_DQ[16]

M0_DQ[19]

M1_DQ[23]

M0_DQ[15]

M1_DQ[0]

DDR_0_D[21]

DDR_1_D[27]

DDR_MEM_CAS

M1_DQ[5]

M0_DQ[22]

DDR_MEM_WE

M0_DQS[3]

DDR_0_D[0]

M0_DQ[0]

DDR_0_DM[2]

M0_DM[2]

DDR_1_D[12]

M1_DQ[12]

DDR_1_D[8]

M1_DQ[8]

DDR_1_DM[0]

M1_DM[0]

M1_DM[2]

DDR_1_DM[2]

@500mA

@500mA

CD-61 (5/12)

BOARD NO. 1-879-612-11

HSC-300_CD-61_011_5

Summary of Contents for HXC-100

Page 1: ...HD COLOR CAMERA HXC 100 SERVICE MANUAL Volume 2 1st Edition ...

Page 6: ......

Page 8: ......

Page 97: ...2 1 HXC 100 V2 J E 2 1 Section 2 Block Diagrams ...

Page 100: ......

Page 104: ......

Page 108: ......

Page 116: ......

Page 130: ......

Page 148: ......

Page 154: ......

Page 170: ......

Page 178: ......

Page 184: ......

Page 205: ......