PCS-G50/G50P

6-5

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

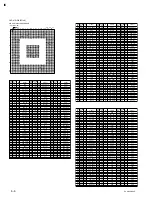

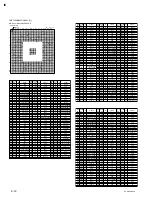

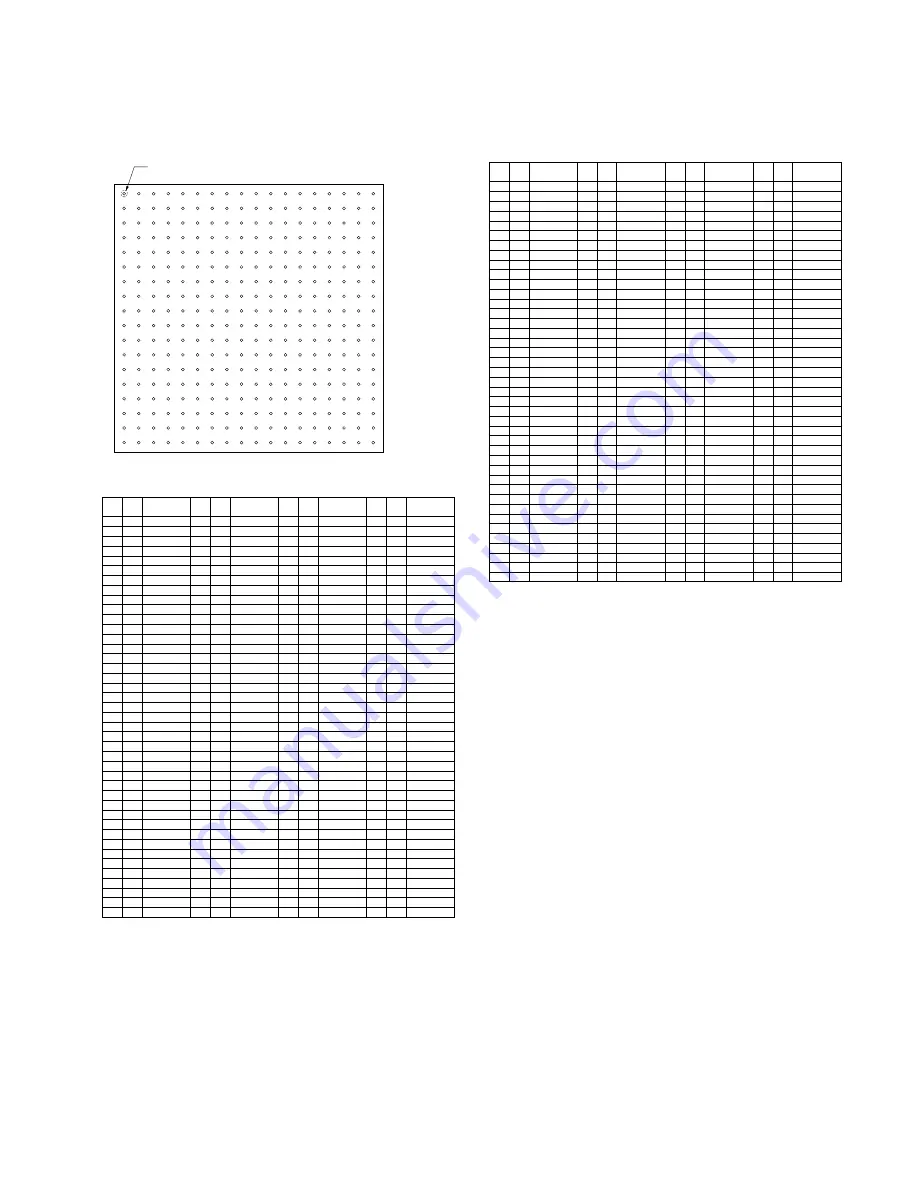

PLD

—BOTTOM VIEW—

INDEX

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

C1

C2

C3

C4

C5

—

—

—

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

—

—

—

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

—

I/O

I/O

I/O

I/O

GND

V

CC

INT

GND

IO

V

CC

IO

IO

IO

IO

IO

IO

IO

IO

IO

V

CC

IO

IO

GND

V

CC

INT

GND

V

CC

INT

GND

IO/DEV OE

IO/

DEV CLR

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

GND

V

CC

INT

GND

IO

IO/INT DONE

IO

IO

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

E1

E2

E3

E4

E5

E6

E7

E8

E9

E10

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

GND

IO

IO

IO/CLKUSR

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

V

CC

IO

IO

IO

IO

IO

IO

IO

IO

V

CC

IO

IO

E11

E12

E13

E14

E15

E16

E17

E18

F1

F2

F3

F4

F5

F6

F7

F8

F9

F10

F11

F12

F13

F14

F15

F16

F17

F18

G1

G2

G3

G4

G5

G6

G7

G8

G9

G10

G11

G12

G13

G14

G15

I/O

—

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

IO

V

CC

IO

IO

IO

IO

IO

IO

V

CC

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

V

CC

IO

IO

IO

IO

IO

IO

IO

IO

IO

G16

G17

G18

H1

H2

H3

H4

H5

H6

H7

H8

H9

H10

H11

H12

H13

H14

H15

H16

H17

H18

J1

J2

J3

J4

J5

J6

J7

J8

J9

J10

J11

J12

J13

J14

J15

J16

J17

J18

K1

K2

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

—

—

—

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I

I

—

—

I

—

—

—

—

—

I/O

I/O

I

I

I

—

—

O

IO

IO

IO

IO

IO

IO

IO

IO

IO

DATA0

GND

GND

V

CC

INT

GND

V

CC

IO

IO

IO

IO

IO

IO

IO

IO/

CSO

CONFIG

CLK0

CLK1

V

CC

A

GNDG

CE

GND

V

CC

INT

GND

GND

V

CC

A

IO

IO

CLK2

CLK3

TDI

GNDG

GNDA

CEO

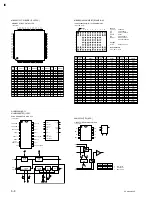

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

K3

K4

K5

K6

K7

K8

K9

K10

K11

K12

K13

K14

K15

K16

K17

K18

L1

L2

L3

L4

L5

L6

L7

L8

L9

L10

L11

L12

L13

L14

L15

L16

L17

L18

M1

M2

M3

M4

M5

M6

M7

I

I/O

I/O

I/O

I

—

—

—

—

—

O

I

I/O

I/O

O

I

I

I/O

I/O

I/O

I/O

I/O

I/O

—

—

—

—

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

MSEL0

IO

IO

IO/ASDO

MSEL1

GND

GND

V

CC

INT

GND

GNDA

TDO

TMS

IO

IO

CONF DONE

TCK

DCLK

IO

IO

IO

IO

IO

IO

GND

V

CC

INT

GND

GND

STATUS

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

V

CC

IO

M8

M9

M10

M11

M12

M13

M14

M15

M16

M17

M18

N1

N2

N3

N4

N5

N6

N7

N8

N9

N10

N11

N12

N13

N14

N15

N16

N17

N18

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

—

I/O

IO

IO

IO

IO

V

CC

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

V

CC

IO

IO

IO

IO

IO

IO

IO

V

CC

IO

IO

IO

V

CC

IO

IO

P13

P14

P15

P16

P17

P18

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15

R16

R17

R18

T1

T2

T3

T4

T5

T6

T7

T8

T9

T10

T11

T12

T13

T14

T15

T16

T17

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

IO

IO

IO

IO

IO

V

CC

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

GND

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

T18

U1

U2

U3

U4

U5

U6

U7

U8

U9

U10

U11

U12

U13

U14

U15

U16

U17

U18

V1

V2

V3

V4

V5

V6

V7

V8

V9

V10

V11

V12

V13

V14

V15

V16

V17

V18

—

—

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

—

—

—

—

I/O

—

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

—

—

—

GND

V

CC

INT

GND

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

GND

V

CC

INT

GND

V

CC

INT

GND

IO

V

CC

IO

IO

IO

IO

IO

IO

IO

IO

IO

V

CC

IO

IO

GND

V

CC

INT

GND

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

PIN

NO.

I/O

SIGNAL

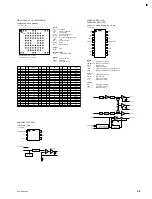

INPUT

CE

CLK0 - CLK3

CLKUSR

CONFIG

DATA0

DCLK

DEV CLR

DEV OE

MSEL0, MSEL1

TCK

TDI

TMS

OUTPUTS

ASDO

CEO

CONF DONE

CSO

INIT DONE

STATUS

TDO

INPUTS/OUTPUTS

IO

OTHER

NC

: CHIP ENABLE

: DEDICATED CLOCK

: OPTIONAL USER-SUPPLIED CLOCK

: CONFIGURATION CONTROL

: DATA

: CLOCK

: CLEAR ON DEVICE

: OUTPUT ENABLE ON DEVICE

: 2-BIT CONFIGURATION

: TEST CLOCK

: TEST DATA

: TEST MODE SELECT

: ACTIVE SERIAL DATA

: CHIP ENABLE

: STATUS

: CHIP SELECT

: STATUS PIN

: STATUS

: TEST DATA

: I/O

: NO CONNECTION

EP1C12F324C8N(300) (ALTERA)

IC

Summary of Contents for Ipels PCS-G50

Page 6: ......

Page 16: ......

Page 26: ......

Page 34: ......

Page 170: ......

Page 186: ......

Page 191: ...PCS G50 G50P 8 7 8 7 CPU 382 B SIDE SUFFIX 12 13 A B C D 1 2 3 4 CPU 382 CPU 382 ...

Page 198: ......

Page 199: ......

Page 200: ...Printed in Japan Sony Corporation 2005 6 22 2005 PCS G50 UC PCS G50P CE E 9 968 181 01 ...