PCS-G50/G50P

6-11

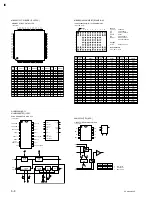

–DRIVER–

1

2

3

4

8

7

6

5

A

B

Z

Y

V

CC

R

D

GND

R

D

A

B

Z

Y

2

3

8

7

6

5

–RECEIVER–

INPUT

D

H

L

OPEN

OUTPUTS

Y

H

L

L

Z

L

H

H

OUTPUTS

R

H

?

L

H

DIFFERENTIAL INPUTS

A

_

B

V

ID

>

50 mV

_

50 mV < V

ID

< 50 mV

V

ID

<

_

50 mV

OPEN

: HIGH LEVEL

: LOW LEVEL

: INDETERMINATE

H

L

?

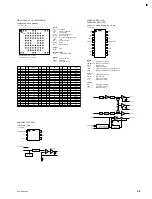

HIGH SPEED DIFFERENTIAL LINE DRIVER/RECEIVER

—TOP VIEW—

SINGLE BUS BUFFER GATE WITH 3-STATE OUTPUT

GND

A

OE

1

2

3

Vcc

4

Y

5

—TOP VIEW—

OE

0

0

1

OUTPUT

A

1

0

X

Y

1

0

HI-Z

0 : LOW LEVEL

1 : HIGH LEVEL

X

: DON'T CARE

HI-Z : HIGH INPEDACE

INPUT

OE

A

Y

4

1

2

DUAL BUS BUFFER GATE WITH 3-STATE OUTPUT

—TOP VIEW—

XOE

1

1

0

OUTPUT

XA

1

0

X

XY

1

0

HI-Z

0 : LOW LEVEL

1 : HIGH LEVEL

X

: DON'T CARE

HI-Z : HIGH INPEDACE

INPUT

1OE

1A

1Y

6

1

2

2OE

2A

2Y

3

7

5

1OE

1A

2Y

GND

1

2

3

4

8

7

6

5

V

CC

2OE

1Y

2A

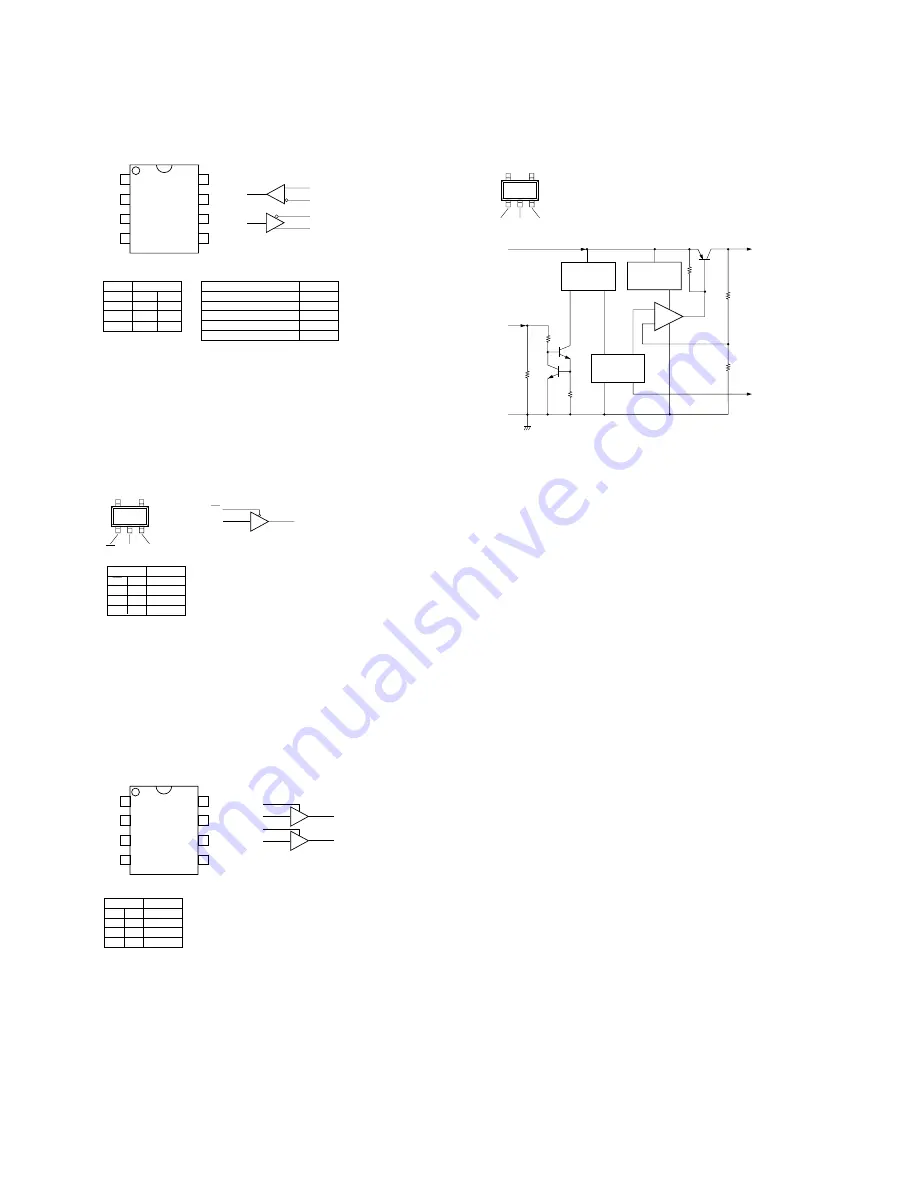

LOW DROPOUT LINEAR REGULATOR

N

P

GND

1

2

3

4

V

OUT

V

IN

V

CONT

5

—TOP VIEW—

V

IN

V

CONT

GND

500 k

Z

320 k

Z

V

OUT

N

P

4

3

OVER HEAT AND

OVER CURRENT

PROTECTION

CONTROL

CIRCUIT

BANDGAP

REFERENCE

+

_

5

1

2

SN65LVDS179DGKR (TI)

SN74LVC1G125DCKR (TI)

SN74LVC2G126DCUR (TI)

TK11133CSCL-G (TOKO)

IC

Summary of Contents for Ipels PCS-G50

Page 6: ......

Page 16: ......

Page 26: ......

Page 34: ......

Page 170: ......

Page 186: ......

Page 191: ...PCS G50 G50P 8 7 8 7 CPU 382 B SIDE SUFFIX 12 13 A B C D 1 2 3 4 CPU 382 CPU 382 ...

Page 198: ......

Page 199: ......

Page 200: ...Printed in Japan Sony Corporation 2005 6 22 2005 PCS G50 UC PCS G50P CE E 9 968 181 01 ...