PCS-G50/G50P

6-13

414

415

416

417

418

419

420

421

422

423

424

425

426

427

428

429

430

431

432

433

434

435

436

437

438

439

440

441

442

443

444

445

446

447

448

449

450

451

452

453

454

455

456

457

458

459

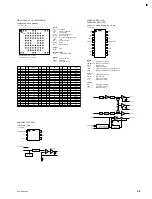

VP2D_18

VP2D_14

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

GND

GND

V

CC

GND

GND

V

CC

GND

GND

V

CC

GND

V

CC

V

CC

V

CC

GND

V

CC

GND

GND

V

CC

GND

GND

V

CC

GND

GND

V

CC

GND

V

CC

V

CC

V

CC

GND

V

CC

GND

GND

V

CC

GND

GND

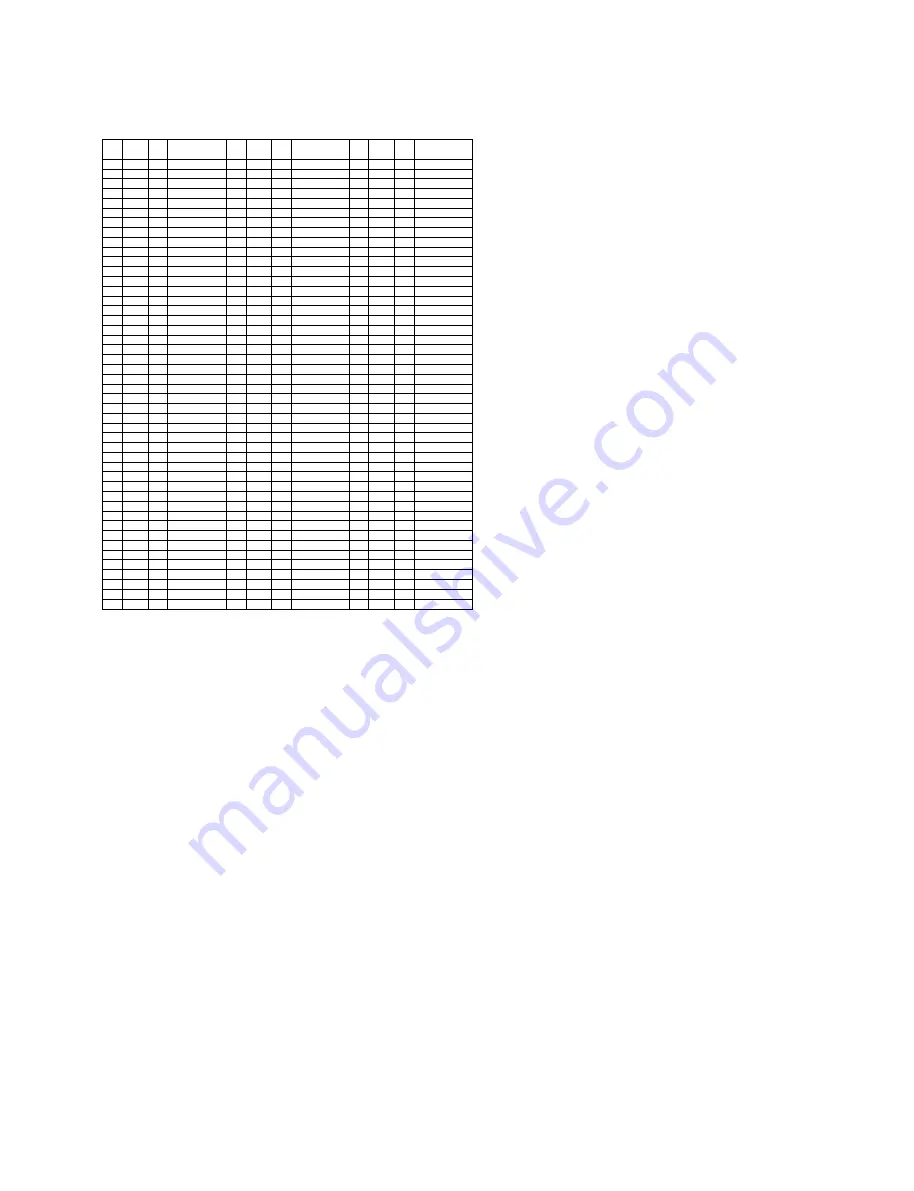

PIN

NO.

E12

E11

E10

E9

E8

E7

E6

F6

G6

H6

J6

K6

L6

M6

N6

P6

R6

T6

U6

V6

W6

Y6

AA6

AA7

AA8

AA9

AA10

AA11

AA12

AA13

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

Y21

W21

V21

U21

T21

R21

P21

N21

OUTER

NO.

I/O

I/O

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

M21

L21

K21

J21

H21

G21

F21

F20

F19

F18

F17

F16

F15

F14

F13

F12

F11

F10

F9

F8

F7

G7

H7

J7

K7

L7

M7

N7

P7

R7

T7

U7

V7

W7

Y7

Y8

Y9

Y10

Y11

Y12

Y13

Y14

Y15

Y16

Y17

Y18

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Y19

Y20

W20

V20

U20

T20

R20

P20

N20

M20

L20

K20

J20

H20

G20

G19

G18

G17

G16

G15

G14

G13

G12

G11

G10

G9

G8

M12

N12

P12

R12

R13

R14

R15

P15

N15

M15

M14

M13

N13

P13

P14

N14

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

I/O

SIGNAL

V

CC

GND

GND

V

CC

GND

V

CC

V

CC

V

CC

GND

V

CC

GND

GND

V

CC

GND

GND

V

CC

GND

GND

V

CC

GND

V

CC

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

NC

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

OUTER

NO.

I/O

SIGNAL

V

CC

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

V

CC

GND

V

CC

GND

V

CC

GND

V

CC

GND

V

CC

GND

V

CC

GND

V

CC

GND

V

CC

GND

OUTER

NO.

I/O

SIGNAL

460

461

462

463

464

465

466

467

468

469

470

471

472

473

474

475

476

477

478

479

480

481

482

483

484

485

486

487

488

489

490

491

492

493

494

495

496

497

498

499

500

501

502

503

504

505

PIN

NO.

506

507

508

509

510

511

512

513

514

515

516

517

518

519

520

521

522

523

524

525

526

527

528

529

530

531

532

661

662

663

664

665

666

667

668

669

670

671

672

673

674

675

676

PIN

NO.

INPUTS

AARDY

AECLKIN

AHOLD

CLKIN

CLKMODE0, CLKMODE1

CLKS0, CLKS1

DR0, DR1

EXT_INT4 - EXT_INT7

HAS

HCNTL0, HCNTL1

HCS

HDS1

,

HDS2

HHWIL

HR/

W

LENDIAN

MAC_EN

MCOL

MCRS

MRCLK

MRXD0 - MRXD3

MRXDV

MRXER

MTCLK

NMI

PCI_EN

PCLK

PGNT

PIDSEL

PRST

RESET

STCLK

TCK, TDI, TMS,

TRST

TINP0, TINP1

VP0CLK0 - VP2CLK0

XSP_DI

: ASYNCHRONOUS MEMORY READY

: EMIFA EXTERNAL CLOCK

: EMIFA HOLD REQUEST

: CLOCK

: CLOCK MODE SELECT

: McBSP EXTERNAL CLOCK SOURCE

: McBSP RECEIVE DATA

: EXTERNAL INTERRUPT

: HOST ADDRESS STROBE

: HOST CONTROL

: HOST CHIP SELECT

: HOST DATA STROBE

: HOST HALF WORD SELECT

: HOST READ/WRITE SELECT

: DEVICE ENABLE MODE

: MAC ENABLE SELECT

: MII COLLISION SENSE

: MII CARRIER SENSE

: MII RECEIVE CLOCK

: MII RECEIVE DATA

: MII RECEIVE DATA VALID

: MII RECEIVE ERROR

: MII TRANSMIT CLOCK

: NONMASKABLE INTERRUPT

: PCI ENABLE

: PCI CLOCK

: PCI BUS GRANT

: PCI INITIALIZATION DEVICE SELECT

: PCI RESET

: DEVICE RESET

: HARDWARE COUNTER CLOCK

: TEST

: TIMER OR GENERAL PURPOSE

: VIDEO PORT CLOCK

: PCI SERIAL INTERFACE DATA

OUTPUTS

AAOE

AARE

AAWE

ABE0

-

ABE7

ABUSREQ

ACE0

-

ACE3

AEA3 - AEA22

AECLKOUT1, AECLKOUT2

AHOLDA

AMUTE0

APDT

ASADS

ASDCAS

ASDCKE

ASDRAS

ASDWE

ASOE

ASOE3

ASRE

ASWE

CLKOUT4, CLKOUT6

DX0, DX1

HINT

HRDY

MTXD0 - MTXD3

MTXEN

PINTA

PREQ

TDO

TOUT0, TOUT1

VDAC

XSP_CLK

XSP_CS

XSP_DO

: EMIFA ASYNCHRONOUS MEMORY OUTPUT ENABLE

: EMIFA ASYNCHRONOUS MEMORY READ ENABLE

: EMIFA ASYNCHRONOUS MEMORY WRITE ENABLE

: EMIFA BYTE ENABLE CONTROL

: EMIFA BUS REQUEST

: EMIFA MEMORY SPACE ENABLE

: EMIFA EXTERNAL ADDRESS

: EMIFA CLOCK

: EMIFA HOLD REQUEST ACKNOWLEDGE

: McASP MUTE

: EMIFA PERIPHERAL DATA TRANSFER

: PROGRAMMABLE SYNCHRONOUS INTERFACE ADDRESS STROBE

: SDRAM COLUMN ADDRESS STROBE

: EMIFA SDRAM CLOCK ENABLE

: SDRAM ROW ADDRESS STROBE

: SDRAM WRITE ENABLE

: PROGRAMMABLE SYNCHRONOUS INTERFACE OUTPUT ENABLE

: EMIFA SYNCHRONOUS MEMORY OUTPUT ENABLE

: PROGRAMMABLE SYNCHRONOUS INTERFACE READ ENABLE

: PROGRAMMABLE SYNCHRONOUS INTERFACE WRITE ENABLE

: CLOCK

: McBSP TRANSMIT DATA

: HOST INTERRUPT FROM DSP

: HOST READY FROM DSP

: MII TRANSMIT DATA

: MII TRANSMIT ENABLE

: PCI INTERRUPT

: PCI BUS REQUEST

: TEST

: TIMER

: VXCO INTERPOLATED CONTROL

: PCI SERIAL INTERFACE CLOCK

: PCI SERIAL INTERFACE CHIP SELECT

: PCI SERIAL INTERFACE DATA

INPUTS/OUTPUTS

ACLKR0

ACLKX0

AD0 - AD31

AED0 - AED63

AFSR0

AFSX0

AHCLKR0

AHCLKX0

AMUTEIN0

AXR0_0 - AXR0_7

CLKR0, CLKR1

CLKX0, CLKX1

EMU0 - EMU11

FSR0, FSR1

FSX0, FSX1

GP0_0 - GP0_15

HD0 - HD31

MDCLK

MDIO

PCBE0

-

PCBE3

PDEVSEL

PFRAME

PIRDY

PPAR

PPERR

PSERR

PSTOP

PTRDY

SCL0

SDA0

VP0CLK1, VP1CLK1, VP2CLK1

VP0CTL0 - VP0CTL2,

VP1CTL0 - VP1CTL2,

VP2CTL0 - VP2CTL2

VP0D_0 - VP0D_19,

VP1D_0 - VP1D_19,

VP2D_0 - VP2D_19

OTHERS

PCIEEAI

PCI66

: McASP RECEIVE BIT CLOCK

: McASP TRANSMIT BIT CLOCK

: PCI DATA ADDRESS BUS

: EMIFA EXTERNAL DATA

: McASP RECEIVE FRAME SYNC OR LEFT/RIGHT CLOCK

: McASP TRANSMIT FRAME SYNC OR LEFT/RIGHT CLOCK

: McASP RECEIVE HIGH FREQUENCY MASTER CLOCK

: McASP TRANSMIT HIGH FREQUENCY MASTER CLOCK

: McASP MUTE

: McASP TX/RX DATA

: McBSP RECEIVE CLOCK

: McBSP TRANSMIT CLOCK

: EMULATION PIN

: McBSP RECEIVE FRAME SYNC

: McBSP TRANSMIT FRAME SYNC

: GENERAL PURPOSE I/O

: HOST PORT DATA

: MDIO SERIAL CLOCK

: MDIO SERIAL DATA

: PCI COMMAND/BYTE ENABLE

: PCI DEVICE SELECT

: PCI FRAME

: PCI INITIATOR READY

: PCI PARITY

: PCI PARITY ERROR

: PCI SYSTEM ERROR

: PCI STOP

: PCI TARGET READY

: I2C CLOCK

: I2C DATA

: VIDEO PORT CLOCK

: VIDEO PORT CONTROL

: VIDEO PORT DATA

: PCI EEPROM AUTO INITIALIZATION

: PCI FREQUENCY SELECT

IC

Summary of Contents for Ipels PCS-G50

Page 6: ......

Page 16: ......

Page 26: ......

Page 34: ......

Page 170: ......

Page 186: ......

Page 191: ...PCS G50 G50P 8 7 8 7 CPU 382 B SIDE SUFFIX 12 13 A B C D 1 2 3 4 CPU 382 CPU 382 ...

Page 198: ......

Page 199: ......

Page 200: ...Printed in Japan Sony Corporation 2005 6 22 2005 PCS G50 UC PCS G50P CE E 9 968 181 01 ...