PCS-G50/G50P

3-6

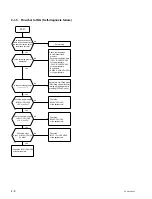

3-2. Circuit Description of PCS-PG50/

PG50P

The following describes the functions of each circuit block

of PCS-PG50/PG50P.

CPU Block [CPU-382]

This block, comprising a CPU, flash memory, SDRAM,

SRAM, Disk On Chip, system/bus controller, buffers,

serial interface for debugging and an RTC, controls the

overall system including optional products.

Video In Block [DSP-113]

This block comprises two sets of video input buffer, video

decoder and noise reduction IC. Analog video input signals

(YC IN and Composite IN) are converted to digital signals,

Y/C separated, decoded from chrominance signals to U/V

signals, and are then output to the VIA block through the

noise reduction IC as 8-bit digital data (ITU-R656 format).

This block also selects input signals.

Video Pre-processing Block [DSP-113]

This block comprises two sets of video input ASIC and

SDRAM. The ASIC, incorporating Temporal Filter and

Scaller, performs pre-filtering for compression and coding

of signals from the Video In block, and then outputs the

signals to the Video FPGA block. The ASIC also functions

as a host interface for reading/writing still pictures. This

block also controls the video decoders through the I2C

interface.

Video FPGA Block [DSP-113]

This block, comprising an FPGA and SDRAM, controls

input signals from the VIA block, input/output signals

from/to the CODEC block, and output signals to the video

Display (1) Block and Audio FPGA block (7 inputs, 6

outputs). This block has functions to combine two screens

and output a video signal.

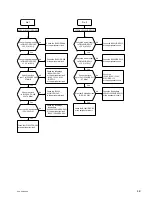

Video Display (1) Block [CPU-382]

This block, comprising a video display IC and SDRAM,

has a “PinP” display function for two video input signals

from the Video FPGA block, and a host interface function

for reading/writing still pictures. This block also transfers

signals to the video Display (2), Audio FPGA and CODEC

blocks.

Video Display (2) Block [CPU-382]

This block, comprising a video output ASIC and SDRAM,

has a graphics (menu) and still picture display function that

overlays graphics onto moving/still picture video signals.

This block also controls the video encoders (MONITOR

OUT) through the I2C interface.

Audio FPGA Block [CPU-382]

This block, comprising an FPGA, controls communication

between the Echo Canceller block and the CPU, data

communication with PCSA-A7 (echo cancelling

microphone), and auto-transmission of the boot program.

This block has a function to select four video input signals

from the Video FPGA, video Display (1) (2 inputs) and

video Display (2) blocks and to output four signals (video

encoder: 2, graphic accelerator: 2). This block also controls

the RTC through the I2C interface.

RGB Display Block [CPU-382]

This block, comprising a graphic accelerator and SDRAM,

has functions to display graphics and still pictures and to

overlay video input signals from the Audio FPGA block.

Analog R/G/B output signals (XGA) and NTSC/PAL

output signals can be displayed, but either one of the

signals is output. The NTSC/PAL signals are transferred to

the video selector and video amplifier in the Video Out

block.

Video Out Block (MONITOR VIDEO OUT)

[CPU-382]

This block comprises two video encoders, video selectors,

video amplifiers and video drivers. The 8-bit digital video

input signals (ITU-R656 format) from the Audio FPGA

block are encoded by the video encoder, converted to

analog signals, and are input to the video selectors together

with the signals from the RGB Display block. Three video

signals are selected and are then output to the data solution

box (PCSA-DSB1S) and to external units through the

amplifiers and drivers.

Summary of Contents for Ipels PCS-G50

Page 6: ......

Page 16: ......

Page 26: ......

Page 34: ......

Page 170: ......

Page 186: ......

Page 191: ...PCS G50 G50P 8 7 8 7 CPU 382 B SIDE SUFFIX 12 13 A B C D 1 2 3 4 CPU 382 CPU 382 ...

Page 198: ......

Page 199: ......

Page 200: ...Printed in Japan Sony Corporation 2005 6 22 2005 PCS G50 UC PCS G50P CE E 9 968 181 01 ...