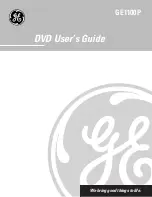

MCE-SV7

13

13

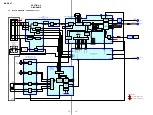

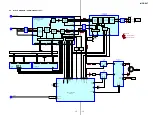

6-2.

BLOCK DIAGRAM – AUDIO/VIDEO Section –

PROGRAM ROM

IC510

• SIGNAL PATH

: CD PLAY (AUDIO)

: CD PLAY (VIDEO)

D/A

CONVERTER

INPUT

INTERFACE

CIRCUIT

OSC

BUFFER

IC504

BUFFER

Q502

LOW-PASS

FILER

MODE

CONTROL

TIMING CONTROL/

CLOCK GENERATOR

VIDEO

FREQUENCY

DIGITAL FILTER,

D/A CONVERTER

IC509

MPEG VIDEO/AUDIO DECODER,

VIDEO SIGNAL PROCESSOR

IC505

14

11

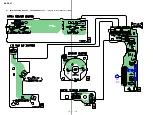

VOUTL

VOUTR

10

RSTB

17

18

19

20

9

7

24

1

DATA

BCK

LRCK

CD-ROM

INTERFACE

CIRCUIT

MPEG

SYSTEM

DECODER

MPEG

VIDEO

DECODER

VIDEO

PROCESS

CIRCUIT

CPU INTERFACE

AUDIO

INTERFACE

CIRCUIT

MPEG

AUDIO

DECODER

D-RAM/ROM INTERFACE

3

4

5

CD-DATA

C2PO

DATA

BCK

LRCK

DATA, BCK,

LRCK, C2PO

CD-BCK

CD-LRCK

6

CD-C2PO

MA0 – MA10

MD0 – MD15

D0

–

D15

D0

–

D15

A0

–

A10

A0

–

A8

384FSO

4

MCKO

X503

27MHz

CT503

MD

XT2

XT1

37

14 13

29

28

38 42 40

60

69

75

113

110

111

108

106

HRDY

Y-OUT

86

DA-XCLK

VCK-IN

DA-DATA

DA-BCK

DA-LRCK

C-OUT

93

114 121

HSEL

112

HD-OUT

119

HD-IN

117

HCK

ML

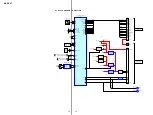

8

MC

LEVEL

SHIFT

IC501

B

(Page 12)

IIC-DATA,

IIC-CLK

D

(Page 14)

MCLK 33.8MHz

A

(Page 12)

DIGITAL

FILTER,

NOISE

SHAPER

CIRCUIT

58 – 56, 54, 52 – 50, 48, 46 – 44

10 – 15, 17, 19, 21, 23 – 29

16 – 19, 22 – 26

A0

–

A10

12 – 5, 27, 26, 23

D8

–

D14

A11 – A17

25, 4, 28, 29, 3, 2, 30

D0

–

D7

O0 – O7

A0 – A10

DQ1 – DQ16

ADDRESS BUS

DATA BUS

D-RAM

IC507

A0 – A8

13 – 15, 17 – 21

2 – 5, 7 – 10, 31 – 34, 36 – 39

WE

22

CE

RAS

LCAS

UCAS

CAS

RESET

HINT

DATA

CLK

RAS0

MWE

MCE

VSYNC/CSYNC

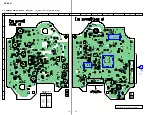

B.P.F.

2

1

4

3

J801

S VIDEO OUT

VIDEO CD CONTROLLER

IC502 (2/2)

88

36

87

20

37

35

85

86

CL680 RESET

CL680 HINT

CL680 HRDY

CL680 SEL

DATAI

CLK1

DATAO

45

VSYNC

DF LATCH

4

CHOMA

LEVEL

22

BGP

30

29

I2C_CLK

I2C_DATA

V. MUTING 65

101

HSYNC

BUFFER

Q501

21

H. SYNC IN

66

DAC RESET

1

VOUT

10 VIN

5

CONT

2

Y IN

15

Y OUT1

14

Y OUT2

6

VOUT

1

VIN

8

TINT

5

BGP

7

C IN

3

RESOLUTION

B.P.F.

C AMP

IC302

Y AMP

IC303

9

C OUT

12

MIX OUT1

11

MIX OUT2

VIDEO OUT

J802

1

MUTE A

8

MUTE B

Q301

Y/C DECODER

IC304

13

XOUT

X501

10MHz

15

XIN

IIC-CLK

IIC-DATA

1

3

VCD L-IN

VCD R-IN

LOW-PASS

FILER

IC101

CN102 (1/2)

SYSTEM

CONTROL 3

TO ST-SV7