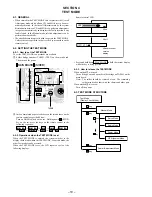

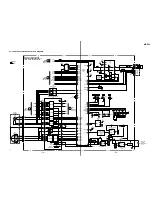

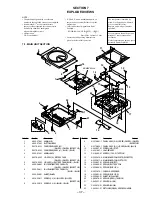

6-2. BLOCK DIAGRAMS

6-2-1. MD BLOCK DIAGRAM

– 17 –

– 18 –

+

–

+

–

+

–

+

–

+

–

+

–

+

–

+

–

+

–

ly

lx

Jx

Jy

A

A

B

C

D

MON

Jx Jy Jx

lx ly lx

a b c d

F

MINIDISC

OPTICAL PICK-UP BLOCK

(LCX-2E)

B

C

D

MON

LD-A

Jy

Jx

lx

ly

VREF

16

15

14

10

9

6

17

7

8

18

5

12

2

1

LD-K

13

AVCC

20

CN501

LD

AVCC

S0

11

19

S0

S1

S1

TRACKING

COIL

AVCC (Q907)

LASER

AUTO POWER

CONTROL

Q501

PD-DRV

XRST

SCK

S BUS

LD-VDD

PD-NI

D

C

B

A

Jy

Jx

Ix

Iy

VREF

D-C

A-C

LD-EMIT

APC

AVCC

(Q907)

TPP/WPP

RF AMP,

FOCUS

ERROR,

TRACKING

ERROR

DFCT

OFTRK

RF OUT

82V

DFCT

OFTRK

ABCD

FE

TE

S MON

PD-I

PD-O

T COUNT

ADIP IN

ADIP

ADIP

T-COUNT

SERIAL

I/F

5

4

13

11

10

9

8

7

3

33

27

26

30

AVCC

38

DVDD

21

39

40

44

41

6

12

RF AMP, FOCUS/TRACKING ERROR AMP

IC501

B+

(Q907)

B+

(Q907)

16

17

28

43

42

24

23

22

27 XRESET

9 ADIP

12 T COUNT

5 TE

MCLK

3 FE

4 ABCD

14 OFTRK

13 DEFECT

7 RF

ID4

ID3

MCK I/O

VDD

98

97

47

XRAS

DRD0

|

DRD3

D0

|

D3

A0

|

A11

DRA0

|

DRA11

63

XOE 60

XCAS 59

XWE

XRAS

54

XOE

XCAS

VSS

VSS

LRCK 39

AUDATA 40

BCK 41

XWE

MCLK 50

BICK

SDATA

LRCK

FF OUT 24

SINT 30

SCK 29

S BUS 28

FR OUT 23

TR OUT 22

TF OUT 21

VDD ADJ

1

VREF

2

20

•

37

•

51

•

75

•

87

52

•

53

•

58

•

57

71

74

•

70

66

•

62

•

65

•

64

IC601

16M DRAM

IC602

9

12

•

15

19

•

21

•

8

•

6

2

•

3

•

24

•

25

5

22

23

14

26

VSS

VSS

1

13

4

B+

(Q907)

SERIAL

INPUT

INTERFACE

8X

INTERPOLATOR

LPF

∆ Σ

MODULATOR

8X

INTERPOLATOR

CLOCK

DIVIDER

LPF

∆ Σ

MODULATOR

1

3

4

5

14

13

AOUTL

AOUTR

11

VREF

16

CKS

10

VDD

2

PD

18BIT D/A CONVERTER

IC302

B+

(Q907)

AOUTL

AOUTR

TF1

TR1

FR1

FF1

VREF

MCLK

SINT

XRST

S MON

PD

SSB CLK

SSB DATA

S0

S1

SERVO,

SYSTEM CONTROL

SECTION

2

SERVO,

SYSTEM CONTROL

SECTION

3

SERVO,

SYSTEM CONTROL

SECTION

4

18

19

20

15

TRK+

TRK–

4

3

FOCUS

COIL

FCS+

FCS–

SERVO,

SYSTEM CONTROL

SECTION

1

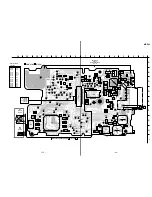

04

MAIN BOARD

(1/2) MD SECTION

• Signal path

: MD

DIGITAL SERVO

ATRAC

MZ-E60

(Page 19)

(Page 19)

(Page 19)

(Page 19)