20

NW-E002F/E003F/E005F

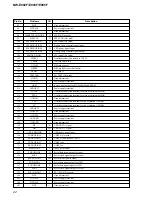

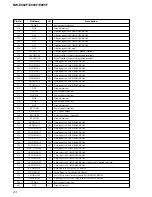

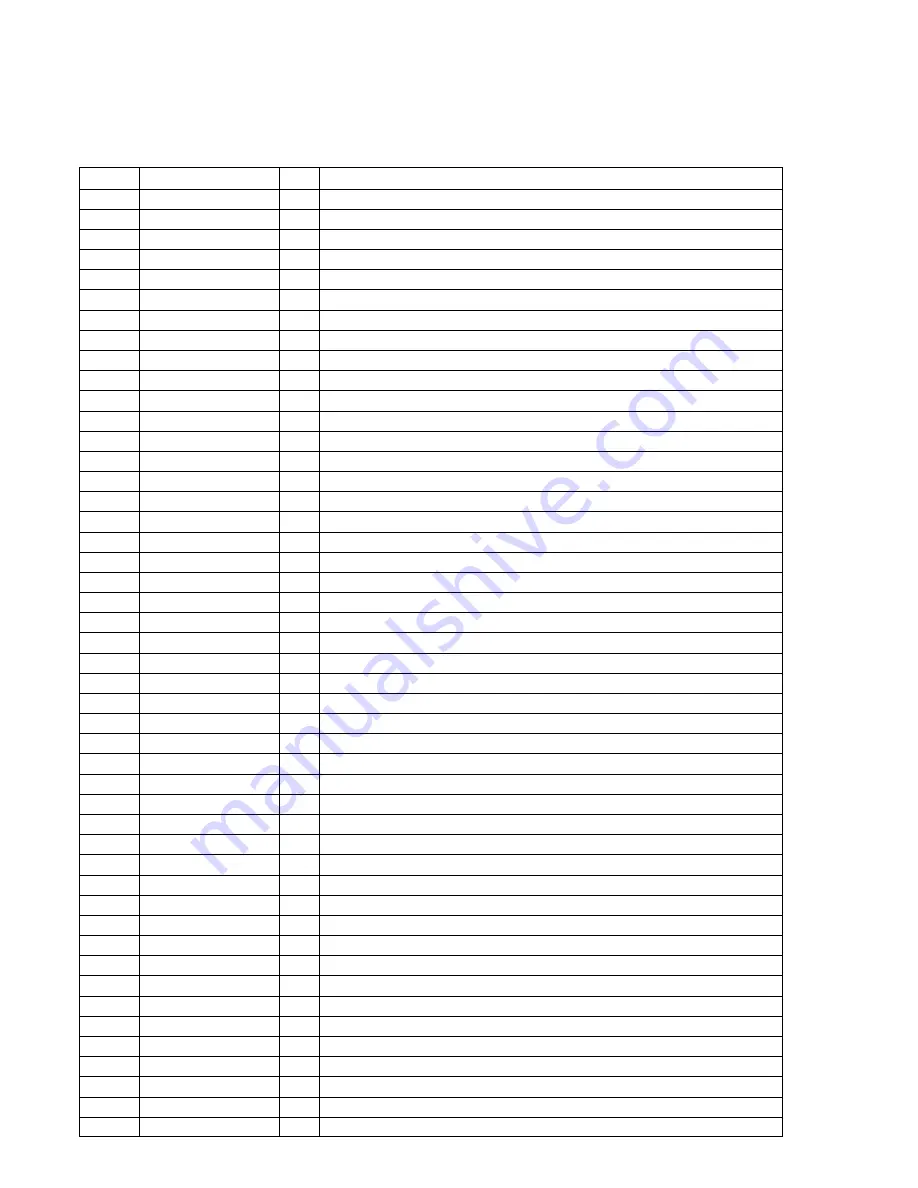

• IC Pin Function Description

MAIN BOARD IC101 CXD5090-003GG

(SYSTEM CONTROLLER, NAND FLASH INTERFACE, USB INTERFACE, A/D, D/A CONVERTER, SERIAL INTERFACE)

Pin No.

Pin Name

I/O

Description

1

NAD0/GPIOC0

I

Data signal

2

NAD1/GPIOC1

I

Data signal

3

NAD2/GPIOC2

I

Data signal

4

NAD3/GPIOC3

I

Data signal

5

NAD4/GPIOC4

I

Data signal

6

NAD5/GPIOC5

I

Data signal

7

NAD6/GPIOC6

I

Data signal

8

NAD7/GPIOC7

I

Data signal

9

NCLE/GPIOC8

O

Command latch enable signal to NAND FLASH ROM

10

NALE/GPIOC9

O

Address latch enable signal to NAND FLASH ROM

11

NCE0/GPIOC10

O

Chip enable signal to NAND FLASH ROM

12

NCE1/GPIOC11

O

Chip enable signal (Not used)

13

NCE2/GPIOC12

O

Chip enable signal (Connected to ground terminal)

14

NCE3/GPIOC13

O

Chip enable signal (Connected to ground terminal)

15

NRE/GPIOC14

O

Read signal to NAND FLASH ROM

16

NWE/GPIOC15

O

Write signal to NAND FLASH ROM

17

NWP/GPIOC16

O

Write protection signal to NAND FLASH ROM

18

NRB0/GPIOC17

O

Read/Busy signal to NAND FLASH ROM

19

NRB1/GPIOC18

O

Read/Busy signal (Not used)

20

NRB2/GPIOC19

O

Read/Busy signal (Connected to +2.8V)

21

NRB3/GPIOC20

O

Read/Busy signal (Connected to +2.8V)

22

DVS

—

Ground terminal

23

DVDIO2

—

Power supply terminal

24

DVDIO2

—

Power supply terminal

25

DVS

—

Ground terminal

26

DVDK2

—

Power supply terminal

27

DVS

—

Ground terminal

28

CRST2

I

Reset signal (Pull down)

29

RST2OUT

O

Reset signal output for Power Control IC

30

RST2VDD

—

Power supply terminal

31

T_ADINL

—

For TEST (Connected to ground terminal)

32

HPVDD

—

Power supply terminal

33

HPOUTL

O

Headphone Lch signal output

34

PVDD

—

Power supply terminal

35

PGND

—

Ground terminal

36

HPOUTR

O

Headphone Rch signal output

37

HPGND

—

Ground terminal

38

GPION0/INT8

I

Wake up signal input

39

GPION1/INT9

I

HOLD key signal input

40

GPION2/INT10

I

Function key signal input

41

GPION3/INT11

I

Function key signal input

42

TDI

I

JTAG data input (Not used)

43

TMS

I

JTAG test mode control signal input (Not used)

44

TCK

I

JTAG clock signal input (Not used)

45

TDO

O

JTAG clock signal output (Not used)

46

TRST

I

JTAG reset input

47

TEST

I

Boot control