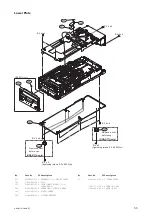

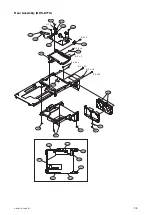

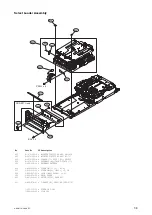

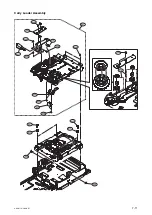

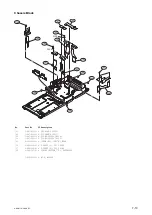

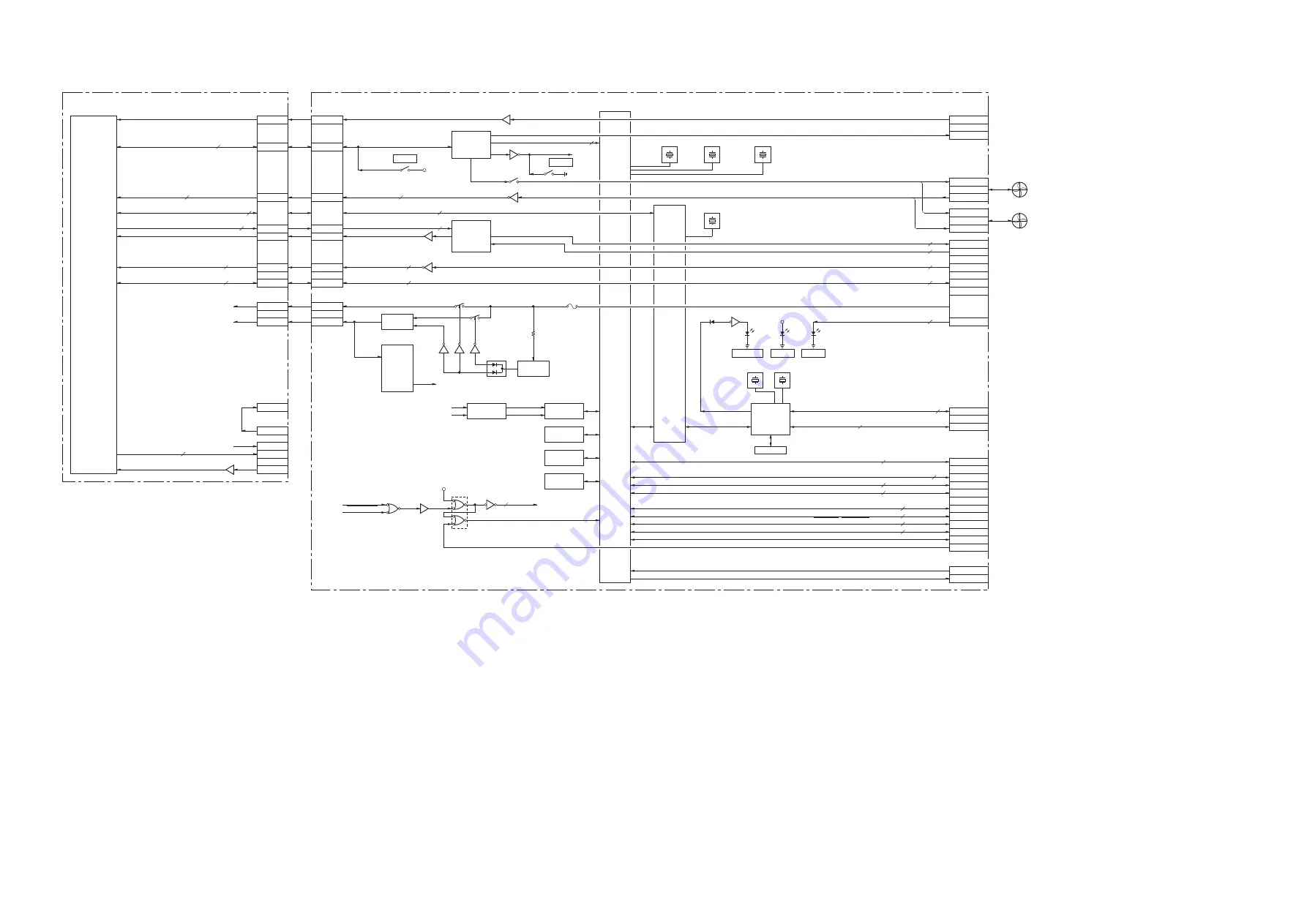

Overall (3/4)

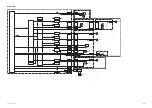

IC700(3/4)

BRIDGE

FPGA

CN700

11

2-8

1,10

13-16

18-21

23-26

28-31

33,35,40

34

36,37

38,39

7

30

33-39

31,40

25-28

20-23

15-18

10-13

1,6,8

7

4,5

2,3

CN2

2

16

3

2

2

K7_UART_RX

K7_SPARE2,K7_UART_TX,FAN_CNT,

USB-SATA_RST,USB_EXIST,

USB2.0,USB3.0

FAN_FG,FAN_FG2

PCIe1/2/3_RX_P/N,PCIe1/2_/3TX_P/N

DEV0_PCIe0_RX_P/N,DEV0_PCIe0_TX_P/N

ADI_RX,ADI_DRV_SEN_H,ADI_TX_EN_H

ADI_TX

ADI_LIB_SEN_H,ADI_RESET_H

LDI/ADI_Select_L,ADI_WRAP-

CN512

1-3

14-20

+12V

+5V

18-20

1-7

CN512

CN11

1

CN10

1

NC

NC

CN717

7

3-6

2

+3.3V

DISC_IN,

ERROR,ACCESS

3

IC714

EJECT

BD-44(3/4)

NC

FC-116

K7_UART_RX

IC8

BUS

TRANSCEIVER

S2

EJECT

+1.8V

K7_SPARE2

FAN_FG/FG2

2

BD_PCIe0/1/2/3_RX_P/N,

BD_PCIe0/1/2/3_TX_P/N

16

IC13

BD_BOOT_SEL0/1,BD_IRQ

3

IC12

S1

RESET

TO

IC3008

Q13,14

IC14,17

CN4

CN5

CN232

V6_232C_Rx

V6_232C_Tx

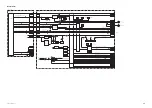

IC3003

100MHz

X3002

125MHz

X3000,3001

66.6MHz

CPU

IC3000

FAN_CNT

FAN_FG

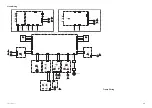

CN1

IC200

TRANSCEIVER

3

ADI_TX_EN_H,

ADI_DRV_SEN_H,ADI_RX

IC202

ADI_TX

IC201

ADI_LIB_SEN_H,

ADI_RESET_H

2

LDI/ADI_Select_L,

ADI_WRAP-

2

IC2000

PCIeSW

IC2001,2002

100MHz

+12V

+5V

IC50

STEP DOWN

REG.

Q2

Q3

IC10,11,15,

STEP DOWN

DC-DC

CONVERTER

18,25,33

+1.8V

+2.5V

+3.3V

+1.0V

+1.5V

D2

IC1

VOLTAGE

DETECTOR

F1

Q7,8

Q4

Q6

/-

ADI_DRV_SEN_L

/-

ADI_LIB_SEN_L,

ADI_RESET_L

LDI/ADI_Select_L,

ADI_WRAP-

IC3001,3002

DDR3

IC3004

LATCH

IC3005

FLASH

IC3007

TEMPERATURE

SENSOR

VTTDDR

VTTVREF

IC16

LDO

+3.3V

+1.5V

IC3010

IC3011-3013

RESET

6

CPU_TRST

TO

IC1000,2000,3000,

3001,3002,3005

+1.5V

IC3006,3009

IC3008

SELF_RESET

HRESET_REQ

FROM

IC12

FROM

IC3000

3

2

2

2

2

IC1004

D1000,

D1001,

D1002

D201

D200

LINK(FC)

POWER

STATUS

D202

+5V

CN1000

+12V

LED_RED/GREEN

1

2

4

3

4

3

25,26,28

22,23

30,32

34,36

1-3,

10,11,

18-20

38,39

2-8

12,13,18,19

IC1000

PCIe

IC1002

212.5MHz

IC1001

100MHz

4

IC1003

S-FLASH

CN3000

3-8

9-15

16,17

18,19

20-25

28-31

33,34

35-38

39

32

6

7

2

2

6

4

2

4

CN233

1

2

NC

NC

FC

DC 12V

ADI IF

DC FAN 1

(52 SQUARE)

DC FAN 2

(52 SQUARE)

NC

+5V_DD

SELF_RESET

7

TX_FAULT_1/DEBUG,RX_LOS_1/DEBUG,

SCL_1,SDA_1,SFP_PR_1,TX_DIS_1,RTSEL_1

X1_RXN/P,

X1_TXP/N

TSEC1_RXD0/1/2/3,

TSEC1_RX_DV/CLK

TSEC1_TXD0/1/2/3,

TSEC1_TX_EN,TSEC1_GTX_CLK/CLK125

EC_MDC,EC_MDIO

IRQ_GbE,RESET_GbE

SDHC_DATA0/1/2/3,

SDHC_CMD/CLK/CD/WP

TDI,TDO,TCK,TMS

CKSTP_IN,CKSTP_OUT

TDI_C,TDO_C,TCK_C,TMS_C

TSEC3_TXD2

TRST

CPU_232C_Rx

CPU_232C_Tx

ODS-D77F

ODS-D77U/ODS-D77F

8-3

Summary of Contents for ODS-D77F

Page 4: ......

Page 7: ...8 Diagrams Block Diagrams 8 1 Frame Wiring 8 5 ODS D77U ODS D77F 3 ...

Page 8: ......

Page 10: ......

Page 42: ......

Page 53: ...Section 3 Maintenance Mode This section will be described soon ODS D77U ODS D77F 3 1 ...

Page 54: ......

Page 80: ......

Page 82: ......

Page 102: ......

Page 103: ......