3-31

PCS-1500/1500P

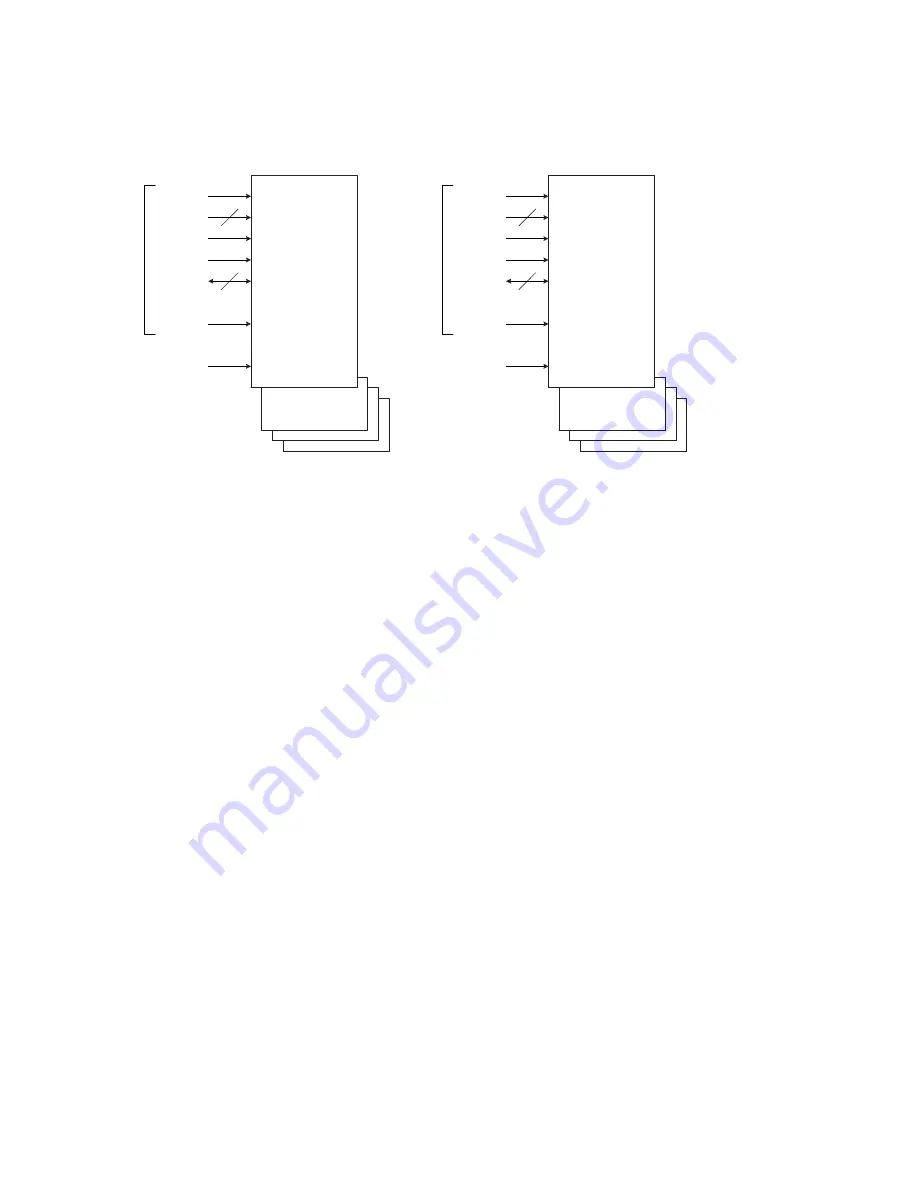

[EC block]

Fig. 3-18 Host Interface of EC Block

The EC block consists of the combination of Echo Canceller DSP1 (IC570) and the 256 kbit-SRAMs

(IC571 to IC573), and the combination of Echo Canceller DSP2 (IC540) and the 256 kbit-SRAMs (IC541

to IC543). The EC block has the function of removing the acoustic echo and suppressing of audio noise.

The 256 kbit-SRAMs (IC571 to IC573, IC541 to IC543) are used for both data and code of the DSPs.

The program code that is required to operate the DSP is downloaded from the CPU and stored in the

256 kbit-SRAMs (IC571 to IC573, IC541 to IC543). The operating clock signal (40 MHz) of the DSP

(IC570, 540) is supplied from the crystal oscillator (X540). Reset is controlled by the “RES_EN” signal

that is supplied from the CPU. (Refer to Fig. 3-18.)

Inputting and outputting of the audio signal to and from the DSPs (IC570, IC540) are performed in the

form of a serial signal. Connection of the serial signal is shown in Fig. 3-17. The serial signal at the AC

block side of Echo Canceller DSP1 (IC570) performs transmission of the before-compressed/coded

(transmission, after echo is removed) audio data to the Audio Codec DSPs (IC520, IC530), and receiving

the decompressed/decoded (receiving) audio data and the other audio data such as ringer tone, etc.

Between the Echo Canceller DSP1 (IC570) and Echo Canceller DSP2 (IC540), the data that is required to

share the processing is sent and received. The serial signal at the AUANA block side performs transmit-

ting and receiving the audio data between the Echo Canceller DSP1 (IC570) and the AD/DA-converter

(IC600).

The clock and frame sync signal of the serial data are supplied from the Serial Timing Generator (IC501).

It operates on the

+

3.3 V-2 power supply voltage.

HA

0

-HA

2

\HRD

HD

0

-HD

7

from/to

CPU BLOCK

2

LVHA1-3

\LVHRD

LVHD0-7

\HCS

\HWR

\LVHWR_P

\HCS_EC

8

256Kbit SRAM

(IC571,572,573)

32Kx8bit x3

\RESET

\RES_EN

Echo Canceller1(IC570)

DSP56303PV80

EXTAL

40MHz

from X540

HA

0

-HA

2

\HRD

HD

0

-HD

7

from/to

CPU BLOCK

2

LVHA1-3

\LVHRD

LVHD0-7

\HCS

\HWR

\LVHWR_P

\HCS_NS

8

256Kbit SRAM

(IC541,542,543)

32Kx8bit x3

\RESET

\RES_EN

EXTAL

40MHz

from X540

Echo Canceller2(IC540)

DSP56303PV80

3-2. Circuit Description of the Respective Boards

Summary of Contents for PCS-1500

Page 8: ......

Page 75: ...1 67 PCS 1500 1500P Sony Corporation Printed in Japan ...

Page 76: ......

Page 130: ......

Page 198: ......