PEGA-CC5

35

35

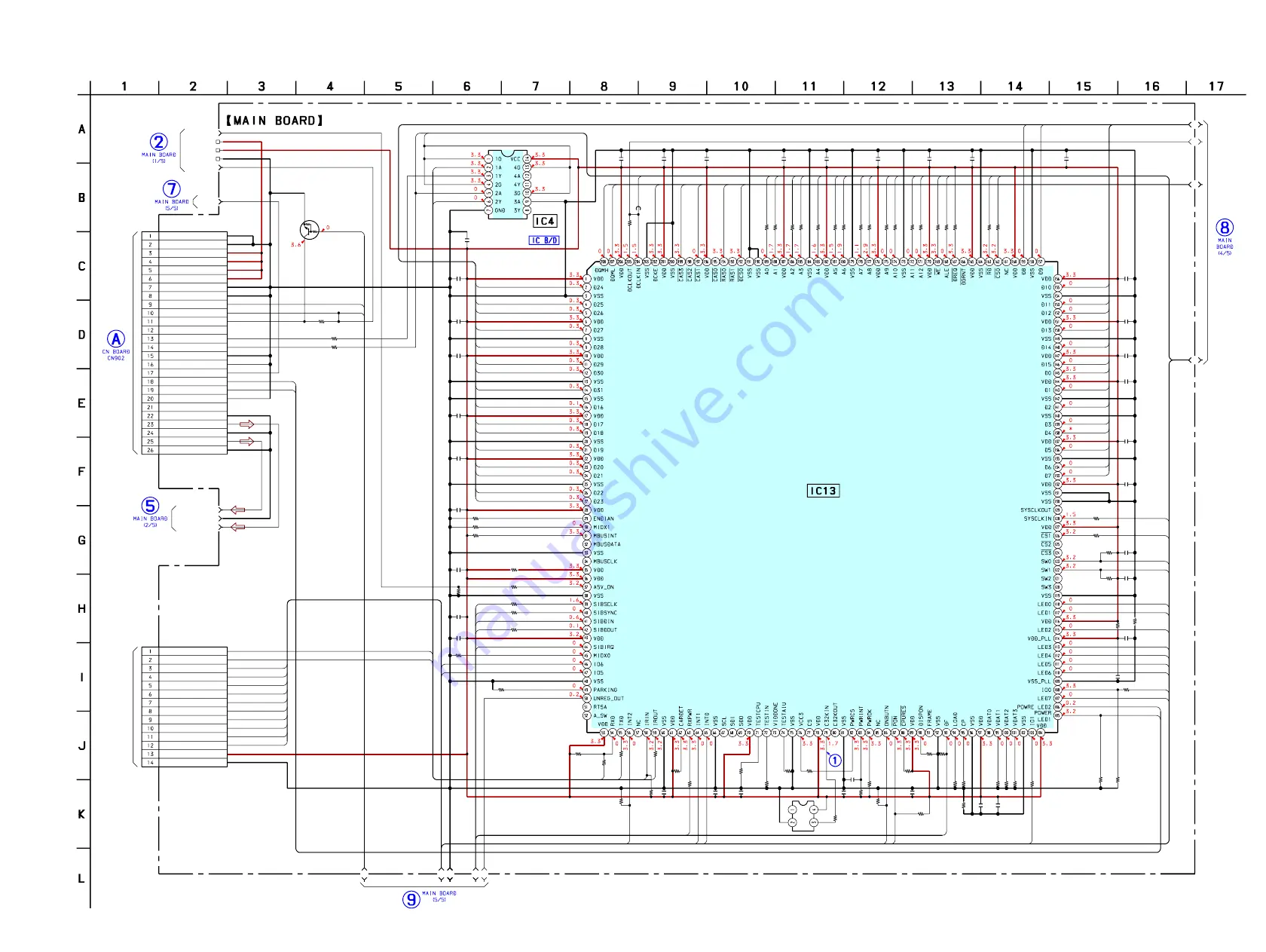

4-6.

SCHEMATIC DIAGRAM – MAIN Board (3/5) –

•

See page 32 for Waveform.

•

See page 42 for IC Block Diagram.

R12

R11

R3

C48

C50

C49

C51

C52

C53

C54

C56

C55

R98

R97

R96

Q3

CN2

CN16

R165

R94

R81

R80

R79

R114

R105

R103

R13

R117

R127

C71

C66

C62

R113

C73

R19

R151

C77

R158

R170

R210

R212

R218

R221

R223

R225

R25

R131

C101

C100

R217

R155 R163

R119

R31

R33

C115

R236

R235

C128

C114

R234

R233

C117

C116

C118

C119

C120

C121

C122

R36

R18

R27

R143

R140

R139

R134

R130

R147

R149

R156

R159

R164

R167

R173

R203

R205

R211

R213

R220

R222

C26

C63

C65

C68

C72

R108

C75

C79

C90

C98

C105

FB105

R14

C83

R109

IC4

X1

R137

R166

R202

R95

R146

22

22

10k

0.01

0.01

0.01

0.01

0.01

0.01

0.01

0.01

0.01

0

100k

10k

DTC144EUA

26P

14P

100k

100k

0

0

0

0

0

0

10k

10k

0

0.01

0.01

0.01

10k

0.01

0

0

0.001

10k

10k

100k

100k

100k

100k

100k

100k

0

0

1

0.01

10

270k 100k

0

100k

100k

0.01

10

10

1

0.01

0

0

0.01

0.01

0.01

0.01

0.01

0.01

0.01

100k

100k

0

22

22

22

22

22

22

22

22

22

22

22

22

22

22

22

10k

22

22

0.1

0.01

0.01

0.01

0.01

0

0.01

0.01

0.01

0.01

0.01

10k

0.01

100k

TC74VHC126FT

32.768KHz

0

10k

100k

0

0

A1

A2

A3

A4

B1

B2

B3

B4

B5

CLIE5.2V

CLIE_AU_GND

CLIE_AU_L

CLIE_AU_R

UNREG

A5V_ON

D3.3V

GND

SIRCS

D

C

K

E

D

C

S

0

C

A

S

1

R

A

S

0

C

A

S

3

D

Q

M

L

D

Q

M

H

SIBDO

SIBSCK

SIBSYN

SIBDIN

SIBIRQ

B

R

E

S

E

T

D

F

1

0

0

TXDB

T

X

D

A

RXDA

T

X

D

B

C

S

0

D

C

L

K

D24

D25

D26

D27

D28

D29

D30

D31

D16

D17

D18

D19

D20

D21

D22

D23

D

8

D

9

D10

D11

D12

D13

D14

D15

D0

D1

D2

D3

D4

D5

D6

D7

W

E

R

D

A

L

E

A

0

A

1

A

2

A

3

A

4

A

5

A

6

A

7

A

8

A

9

A

1

0

A

1

1

A

1

2

IO5

TXDA

CS1

SYSCLK

O

N

B

U

T

N

P

O

N

IO

3

IO

4

IO

2

R

X

D

B

RXDB

LED1

LED2

SW0

SW1

FD0

FD1

FD2

FD3

FD4

FD5

FD6

FD7

FD0

FD1

FD2

FD3

FD4

FD5

FD6

FD7

SW0

SW1

IO6

IO0

IO

1

IO

0

IO

1

HOTSYNC

CHARGE

UNREG

LED1

LED2

RXDA

(3/5)

GND

GND

GND

DC+B

DC+B

DC+B

DC+B

GND

GND

UNREG OUT

HOT SYNC

RXD/CVO

DTR/AVM

TXD/EBI

RTS/AOR

CTS/AOL

CHARGE CONT

GND

LED1

LED2

SIRCS

NC

NC

NC

GND

VCC

RXD

TXD

SW0

SW1

LED0

LED1

LED2

LED3

LED4

LED5

LED6

LED7

BUFFER

INVERTER

SGND

SGND

(NC)

Summary of Contents for PEGA-CC5

Page 61: ...61 PEGA CC5 MEMO ...