4

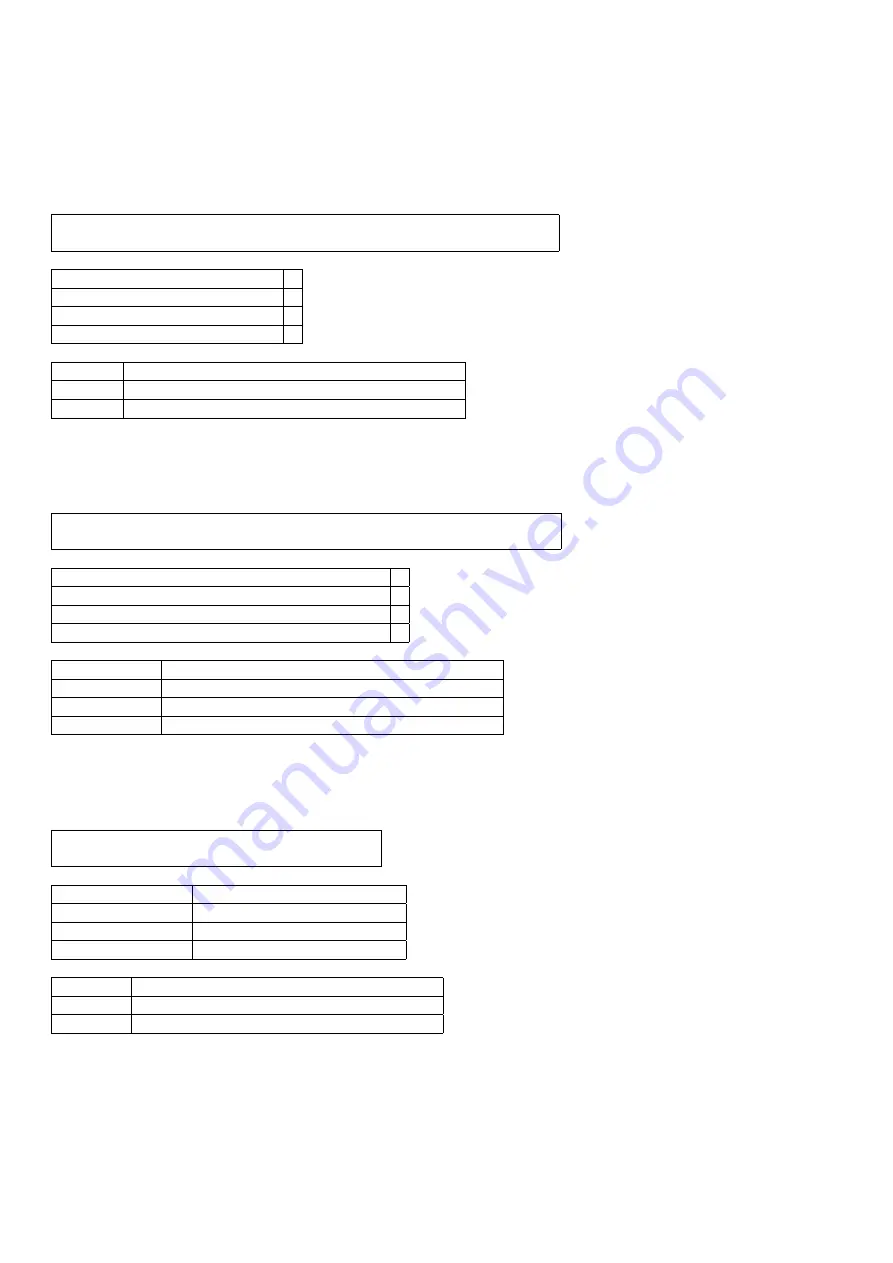

CPU OVERVIEW

32

*1) bit 5 of rs is inverted

VFPU load/store instructions seem to support only 16-byte-aligned accesses (similiar to Altivec and SSE).

4.8.1

lv

lv

LoadVector Quadword Relative to Address in General Purpose Register

fpu_vtr <- vector_at_address ( %gpr)

lv.q %vfpu_rt, offset(%base)

%fpu_rt

VFPU Vector Target Register (column0-31/row32-63)

%base

GPR, specifies Source Address Base

offset

signed Offset added to Source Address Base

Final Address needs to be 64-byte aligned.

4.8.2

sv

sv

StoreVector Quadword Relative to Address in General Purpose Register

vector_at_address ( %gpr) <- fpu_vtr

sv.q %vfpu_rt, offset(%base), cache_policy

%fpu_rt

VFPU Vector Target Register (column0-31/row32-63)

%base

specifies Source Address Base

offset

signed Offset added to Source Address Base

cache_policy

0 = write-through, 1 = write-back

Final Address needs to be 64-byte aligned.

4.8.3

vzero

vzero

SetVectorZero (Single/Pair/Triple/Quad)

vfpu_regs[%vfpu_rt] <- 0.0f

vzero.s %vfpu_rt

Set 1 Vector Component to 0.0f

vzero.p %vfpu_rt

Set 2 Vector Components to 0.0f

vzero.t %vfpu_rt

Set 3 Vector Components to 0.0f

vzero.q %vfpu_rt

Set 4 Vector Components to 0.0f

%vfpu_rt

VFPU Vector Target Register ([s|p|t|q]reg 0..127)

Summary of Contents for PlayStationPortable

Page 114: ...12 AUDIO PROCESSING 114 12 Audio Processing 12 1 Overview 44100 Hz Sample Frequency ...

Page 116: ...14 WLAN 116 14 WLAN ...

Page 117: ...15 USB PORT 117 15 USB Port ...

Page 118: ...16 UMD 118 16 UMD ...

Page 119: ...17 MEMORY STICK 119 17 Memory Stick ...

Page 128: ...21 FLASH MEMORY STRUCTURE FLASH1 128 21 Flash Memory Structure flash1 DIC REGISTRY VSH THEME ...

Page 141: ...28 IPL 141 28 IPL ...