PRS-505

34

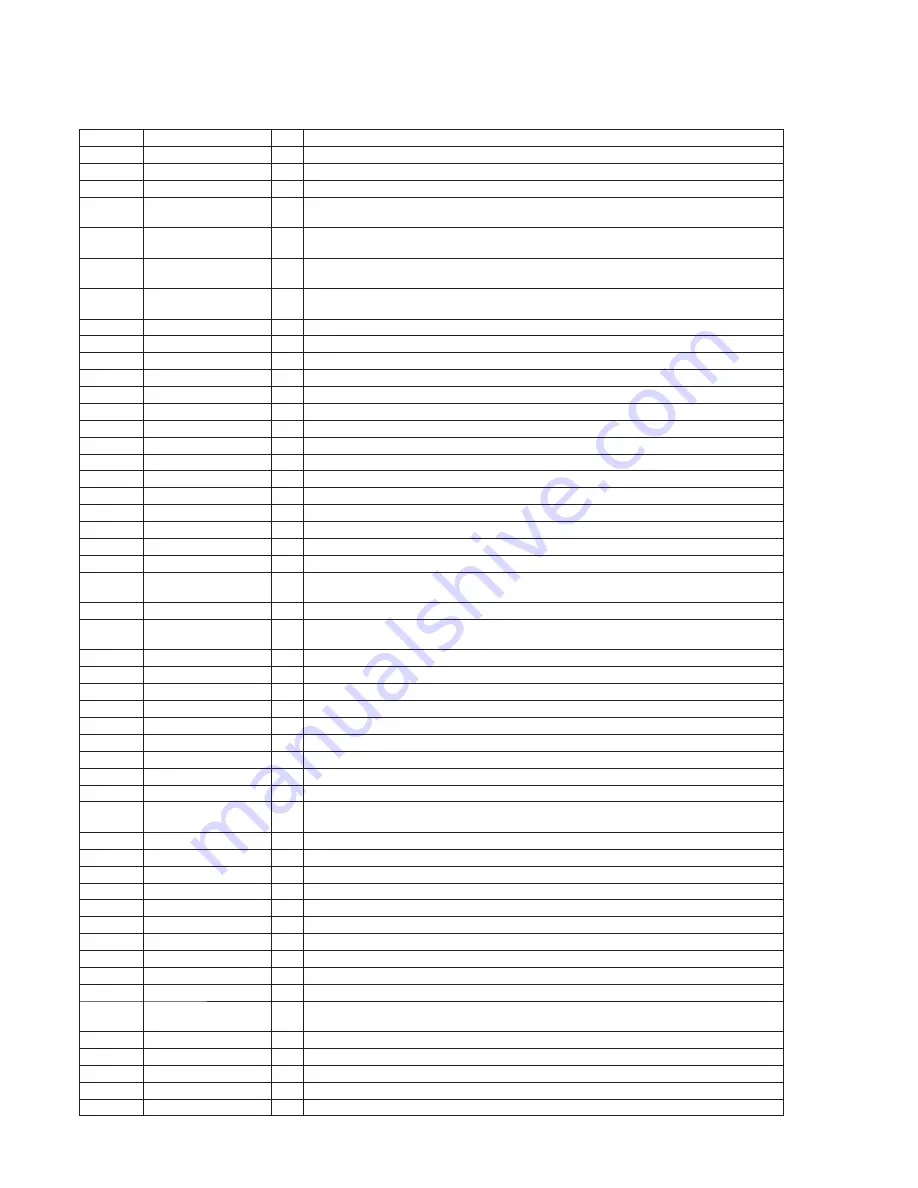

MAIN BOARD IC201 R5C807 (MEMORY STICK DUO/SD MEMORY CARD CONTROLLER)

Pin No.

Pin Name

I/O

Description

1

VCCEN

O

+3.3V power supply control signal output terminal Not used

2

GPIO

I/O

Not used

3

LED

O

Not used

4

HWSPND

I

Hardware suspend mode select signal input from the main CPU

"L": hardware suspend mode

5

RWMODE

I

Read-write timing mode select signal input terminal

"H": maximum cycle time Fixed at "H" in this set

6

WAMODE

I

WAIT/DTACK mode select signal input terminal

"L": DTACK mode, "H": WAIT mode Fixed at "L" in this set

7

LTLEN

I

Little/big endian select signal input terminal

"L": little endian mode, "H": big endian mode Fixed at "L" in this set

8

TEST

I

Test mode terminal Normally

fi

xed at "L"

9

CKIN

I

Host colck signal input from the main CPU

10

GND

-

Ground terminal

11

RST

I

Reset signal input terminal "L": reset

12

VCC_ROUT

-

Power supply terminal (+1.8V)

13

VCC_RIN

-

Power supply terminal (+1.8V)

14

REGEN

I

Internal regulator control signal input terminal "L": regulator on Fixed at "H" in this set

15

INT

O

Interrupt request signal output to the main CPU

16

WAIT/DTACK

O

Data acknowledge signal output terminal Not used

17

WR

I

Write enable signal input from the main CPU

18

RD

I

Read enable signal input from the main CPU

19, 20

EB0, EB1

I

Byte enable signal input terminal Not used

21

VCC_HOST

-

Power supply terminal (+3.3V)

22

CS

I

Chip select signal input from the address decoder

23 to 30

D15 to D8

I/O

Two-way data bus with the USB controller, main CPU, SD-RAM and NOR

fl

ash memory

31 to 33

D7 to D5

I/O

Two-way data bus with the USB controller, main CPU, NAND

fl

ash memory, SD-RAM and

NOR

fl

ash memory

34

GND

-

Ground terminal

35 to 39

D0 to D4

I/O

Two-way data bus with the USB controller, main CPU, NAND

fl

ash memory, SD-RAM and

NOR

fl

ash memory

40

BS

I

Bus cycle start signal input terminal Not used

41

A22

I

Address signal input terminal Not used

42

VCC_ROUT

-

Power supply terminal (+1.8V)

43 to 47

A21 to A17

I

Address signal input terminal Not used

48

VCC_HOST

-

Power supply terminal (+3.3V)

49

A16

I

Address signal input terminal Not used

50 to 64

A15 to A1

I

Address signal input from the main CPU

65

A0

I

Address signal input terminal Not used

66

GND

-

Ground terminal

67

SDCD

I

SD memory card detect signal input from the SD memory card slot

"L": SD memory card slot in

68

SDDAT3

I/O

Two-way 4-bits data bus with the SD memory card slot

69

MDIO11

I/O

Not used

70

MSDAT0

I/O

Two-way data bus with the memory stick duo slot

71

MDIO12

I/O

Not used

72

MSDAT1

I/O

Two-way data bus with the memory stick duo slot

73

VCC_3V

-

Power supply terminal (+3.3V)

74

MDIO13

I/O

Not used

75

MSDAT2

I/O

Two-way data bus with the memory stick duo slot

76

MDIO14

I/O

Not used

77

MSDAT3

I/O

Two-way data bus with the memory stick duo slot

78 to 84

MDIO15, MDIO19 to

MDIO24

I/O

Not used

85

SDWP

I

SD memory card write protect switch signal input from the SD memory card slot

86

VCC_ROUT

-

Power supply terminal (+1.8V)

87

MSCLK

O

Serial clock signal output to the memory stick duo slot

88

MDIO17

I/O

Not used

89

SDCLK

O

Serial clock signal output to the SD memory card slot

• IC Pin Function Description

Summary of Contents for PRS-505

Page 52: ...PRS 505 MEMO 52 ...

Page 73: ...MEMO PRS 505 21 ...