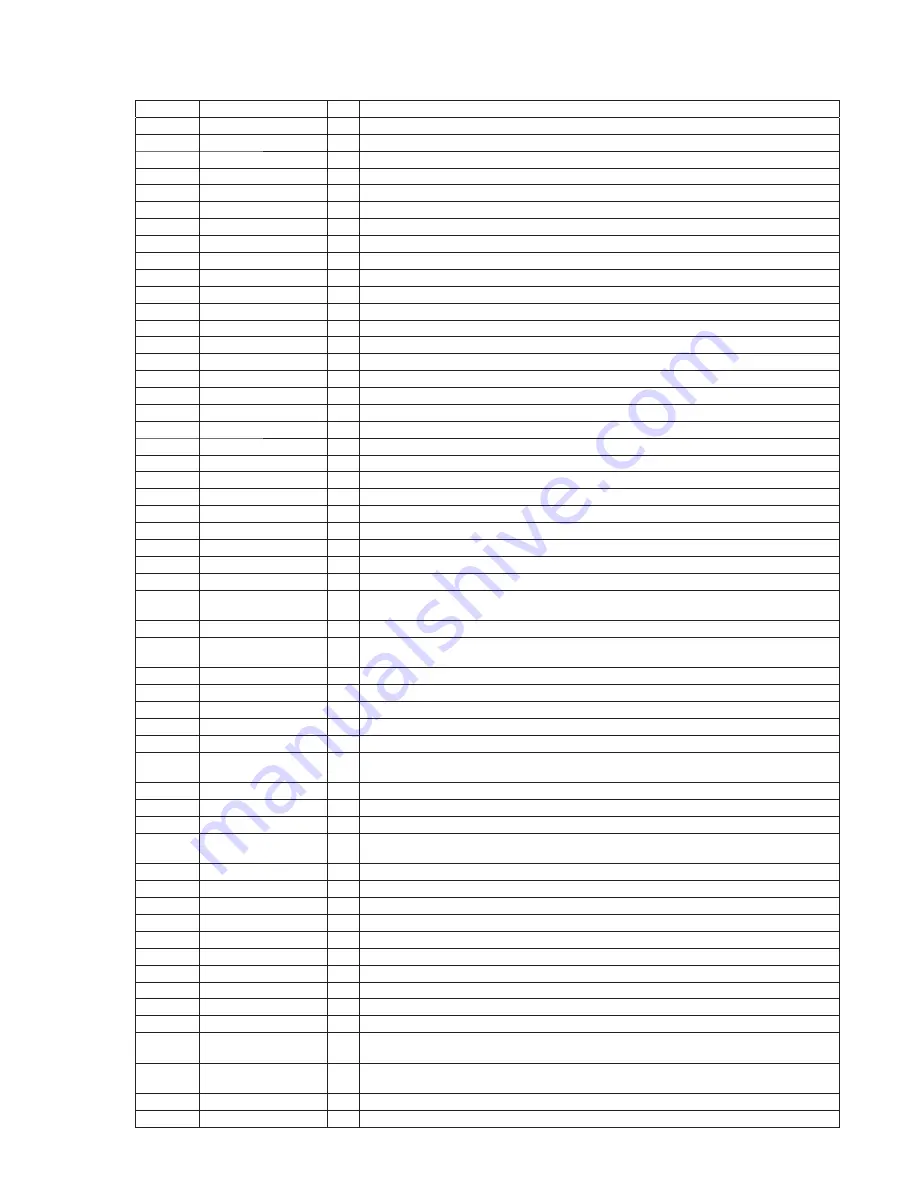

PRS-505

41

Pin No.

Pin Name

I/O

Description

E8

UART1_RXD

I

Serial data input from the sub CPU

E9

UART1_CTS

O

Clear to send signal output to the sub CPU

E10

NAND-CLE

O

Command latch enable signal output to the NAND

fl

ash mamory

E11

PDOE

O

Output enable signal output to the indicator controller

E12

PD10

O

Video data output to the indicator controller

E13

TIN

I

Timer input terminal Not used

E14

PCA3PCORE

O

Regulator control signal output terminal

E15

SRETHER

O

Not used

F1, F2

A20, A19

O

Address signal output to the NOR

fl

ash memory

F3, F4

D28, D27

I/O

Two-way data bus with the SD-RAM

F5, F6

NVDD1

-

Power supply terminal (+2.9V)

F7

PCMSCARD

O

Regulator control signal output terminal

F8

SRUSB20

O

No used

F9

SSI_TXDAT

O

Audio data output to the audio D/A converter

F10

SRSRAM1

O

Not used

F11

QVDD3

-

Power supply terminal (+1.9V)

F12, F13

PD14, PD15

O

Video data output to the indicator controller

F14

USB_CHRG

O

USB charge enable signal output to the sub CPU

F15

SRDSP

O

Reset signal output to the audio D/A converter

G1, G2

A17, A18

O

Address signal output to the NOR

fl

ash memory

G3, G4

D26, D25

I/O

Two-way data bus with the SD-RAM

G5

NVDD1

-

Power supply terminal (+2.9V)

G6

VSS

-

Ground terminal

G7

NVDD4

-

Power supply terminal (+2.9V)

G8 to G10

VSS

-

Ground terminal

G11

PCA3PIO

O

Regulator control signal output terminal

G12

PCUSB11

O

Not used

G13

RSCINT

I

Interrupt request signal input from the memory stick duo/SD memory card controller

G14

MSDET

I

Memory stick duo detect signal input from the memory stick duo slot

"L": memory stick duo slot in

G15

SRMS

O

Not used

H1

A15

O

Address signal output to the memory stick duo/SD memory card controller, SD-RAM and

NOR

fl

ash memory

H2

A16

O

Address signal output to the NOR

fl

ash memory

H3 to H5

D22 to D24

I/O

Two-way data bus with the SD-RAM

H6 to H9

VSS

-

Ground terminal

H10

NVDD2

-

Power supply terminal (+2.9V)

H11

USB_BOOT

I

Main CPU boot mode control signal input from the sub CPU

H12

PCR5C

O

Hardware suspend mode output to the memory stick duo/SD memory card controller

"L": hardware suspend mode

H13

PA14

O

Not used

H14

I2CSDA

I/O

Two-way IIC bus with the temperature sensor

H15

TMS

I

Test mode select signal input terminal Not used

J1, J2

A14, A12

O

Address signal output to the memory stick duo/SD memory card controller, SD-RAM and

NOR

fl

ash memory

J3, J4

D21, D20

I/O

Two-way data bus with the SD-RAM

J5

NVDD1

-

Power supply terminal (+2.9V)

J6, J7

VSS

-

Ground terminal

J8

QVDD1

-

Power supply terminal (+1.9V)

J9

VSS

-

Ground terminal

J10

SRR5C

O

Reset signal output to the memory stick duo/SD memory card controller

J11

I2CSCL

O

IIC bus serial clock signal output to the temperature sensor

J12

TCK

I

Test clock signal input terminal Not used

J13

XTDO

O

Test data signal output terminal Not used

J14, J15

BOOT1, BOOT0

I

System boot mode select signal input terminal

K1

A13

O

Address signal output to the memory stick duo/SD memory card controller, SD-RAM and

NOR

fl

ash memory

K2

A11

O

Address signal output to the memory stick duo/SD memory card controller and NOR

fl

ash

memory

K3

XCS2

O

Chip select signal output to the SD-RAM

K4

D19

I/O

Two-way data bus with the SD-RAM

Summary of Contents for PRS-505

Page 52: ...PRS 505 MEMO 52 ...

Page 73: ...MEMO PRS 505 21 ...