46

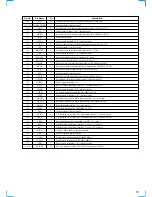

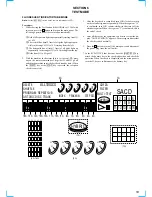

4-25. IC PIN FUNCTION DESCRIPTION

•

MAIN BOARD IC801 CXD2751Q

(DSP DECODER)

Pin No.

Pin Name

I/O

Description

1

XSRQ

O

Data request signal output to the DVD CONVERTER (IC701)

2

XSHD

I

Header flag signal input from the DVD CONVERTER (IC701)

3

VDD

—

Power supply terminal (+3.3V)

4

VSS

—

Ground terminal

5

SDCK

I

Serial data clock signal input from the DVD CONVERTER (IC701)

6

SMUTE

I

Muting signal input from the system controller (IC901) “L”: muting

7

XMSLAT

I

Latch signal input from the system controller (IC901)

8

MSCK

I

Clock signal input from the system controller (IC901)

9

MSDATI

I

I

Serial data input from the system controller (IC901)

10

MSDATO

O

Serial data output to the system controller (IC901)

11

MSREDY

Ready signal input from the system controller (IC901) “L”: ready

12

XMSDOE

O

Data enable signal output terminal Not used (open)

13

XRST

I

Reset signal input from the expander (IC902)

14

MCKI

I

Master clock signal input terminal

15

VSS

—

Ground terminal

16

CK75S

I

Master clock select signal input terminal “L”: 512fs, “H”: 768fs (fixed at “H” in this set)

17

EXCKO1

O

External clock 1 signal output terminal

18

EXCKO2

O

External clock 2 signal output terminal Not used (open)

19

LRCK

I/O

Clock signal input/output terminal (44.1kHz) Not used (open)

20

NC

—

Not used (open)

21

MNT2

O

Monitor 2 signal output terminal Not used (open)

22

TRST

I

Reset signal input terminal (normally: fixed at “L”)

23

TCK

I

Clock signal input terminal for test (normally: fixed at “L”)

24

TDI

I

Data input terminal for test (normally: open)

25

TENA1

I

Data enable signal input terminal for test (normally: open)

26

TDO

O

Data output terminal for test (normally: open)

27

VST

—

Ground terminal for test (normally: fixed at “L”)

28

VDD

—

Power supply terminal (+3.3V)

29

VSS

—

Ground terminal

30

MNT1

O

Monitor 1 signal output terminal Not used (open)

31

MNT0

O

Monitor 0 signal output terminal Not used (open)

32

XBIT

O

Monitor signal output terminal Not used (open)

33

F75HZ

O

Clock output terminal (75Hz) Not used (open)

34

SUPDAT

O

Serial data output terminal Not used (open)

35

XSUPAK

O

Data flag signal output terminal Not used (open)

36

SUPEN

O

Data enable signal output terminal Not used (open)

37

TEST1

I

Test 1 signal input terminal for test (normally: fixed at “L”)

38

VSS

—

Ground terminal

39

TEST2

I

Test 2 signal input terminal for test (normally: fixed at “L”)

40, 41

VSS

—

Ground terminal

42

BCKD

I

Phase reference signal input terminal

43 to 45

NC

—

Not used (open)

46

BCKA

I

Shift clock signal input terminal

47

DSAL

O

DSD data (Lch) output terminal

48

DSAR

O

DSD data (Rch) output terminal

49

ZDFLGL

O

Data (Lch) flag detect signal output terminal Not used (open)

Summary of Contents for SCD-C333ES - Super Audio Cd Changer

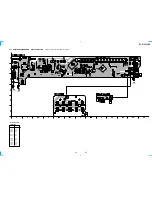

Page 18: ...SCD C333ES 18 18 4 2 SCHEMATIC DIAGRAM RF SECTION Refer to page 40 for Waveforms ...

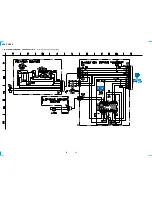

Page 28: ...SCD C333ES 28 28 4 12 SCHEMATIC DIAGRAM AUDIO SECTION 2 3 ...

Page 29: ...SCD C333ES 29 29 4 13 SCHEMATIC DIAGRAM AUDIO SECTION 3 3 ...

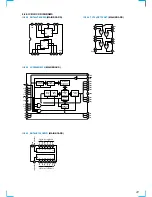

Page 34: ...SCD C333ES 34 34 4 18 SCHEMATIC DIAGRAM HP SECTION ...

Page 36: ...SCD C333ES 36 36 4 20 SCHEMATIC DIAGRAM SENSOR SECTION Refer to page 45 for IC Block Diagram ...

Page 38: ...SCD C333ES 38 38 4 22 SCHEMATIC DIAGRAM POWER SECTION ...