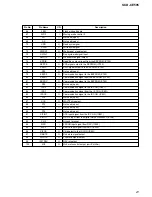

21

SCD-CE595

Pin No.

Pin Name

I/O

Description

66

FEW

I

Flash writing Enable

67

MD2

I

Muving mode control 2

68

PF7

—

Not used (open)

69

AS

—

Not used (open)

70

XDR

O

Reed sycle signal

71

XWR

O

Write sycle signal

72

XWRST

O

Waltz reset signal output

73

XWAIT

I

Bus sycle wait signal input

74

SMUTE

O

Waltz smute signal output

75

EPR/B

I

Read/Busy signal input from the EEPROM (IC702)

76

XEPCE

O

XCS signal output to the EEPROM (IC702)

77

XEWC

O

XWC signal output to the EEPROM (IC702)

78

P32

O

Not used (open)

79

EEPS0

O

Communication signal to the EEPROM (IC702)

80

EEPS1

I

Communication signal from the EEPROM (IC702)

81

EEPSC

O

Communication signal to the EEPROM (IC702)

82

P36

—

Not used (open)

83

IFS0

O

Communication signal to the IS CON (IC801)

84

IFS1

I

Communication signal from the IS CON (IC801)

85

IFSCK

O

Communication signal to the IS CON (IC801)

86

P74

—

Not used (open)

87

XCS

O

WALTZ chip select

88

P72

—

Not used (open)

89

P71

—

Not used (open)

90

P70

—

Not used (open)

91

XIFINT

I

ACK input signal from the IS CON (IC801)

92

XINTO

I

WALTZ input from the Digital Servo Processor (IC706)

93

PG2

—

Ground terminal

94

MZR

I

ZEROR input signal from DAC (IC200)

95

MZL

I

ZEROL input signal from DAC (IC200)

96

XIFCS

O

Chip select to the IS CON (IC801)

97

R MUTE

O

Rch mute signal output

98

L MUTE

O

Lch mute signal output

99

INIT DAC

O

DAC int output

100

M/2

O

Mch mute control output (surr/Cntr/Sw)

Summary of Contents for SCD-CE595

Page 34: ...34 SCD CE595 MEMO ...