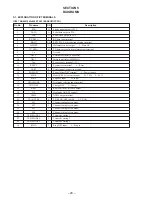

– 20 –

Pin No.

Pin name

I/O

Description

1

STB

O

Strobe signal output to PLL.

2

DATA

O

Serial data output to PLL.

3

CLK

O

Serial clock output to PLL.

4

RX DATA

I

RX data input terminal.

5

SIG IN

I/O

RSSI, PLL-Lock signal input/output terminal.

––––––––––––––––––

6

H-MUTE

O

Half mute control output. L : Mute ON

7

TX DATA

O

TX data, external system alarm output terminal.

8

V

SS

–

Ground.

9

OSC 2

O

External oscillator (4.048MHz).

10

OSC 1

I

Internal oscillator (4.048MHz).

11

V

DD

–

Power supply terminal (+3V).

–––––––––––––––

12

RESET

I

System reset terminal. L : Reset

13

TEST

I

Test terminal (connect to ground).

14

POW-DET

I

Power failuer DET terminal. L : Power failure

15

MBR

I

Make30/40 (%) selection input. H : 30%, L : 40%

16

PAGE

I

Page key input. H : input

17

DIAL MODE

I

Dial mode selection input terminal.

––––––––––––––––––––

18

CHG DET

I

Charge DET. L : Charge

19

RSSI

O

RSSI sensitivity selection output.

20

DP

O

Dial pulse ON/OFF control.

21

DTMF

O

DTMF output terminal.

––––––––––––––––––––––––––

22

TX+B CTRL

I

TX B+ ON/OFF contorl. L : TX ON

23

M 1

I

Channel setting for test mode.

24

M 2

I

Channel setting for test mode.

25

M 3

I

Channel setting for test mode.

26

M 4

I

Channel setting for test mode.

27

TEST MODE 1

I

Test mode setting 1.

28

TEST MODE 2

I

Test mode setting 2.

29

TEST MODE 3

I

Test mode setting 3.

––––––––––––

30

RING

I

Ring DET input. L : Ring in

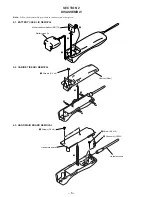

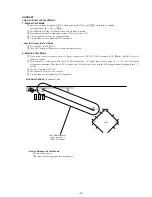

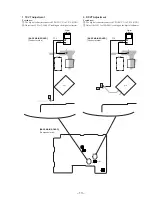

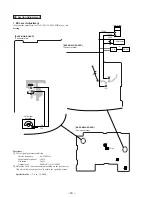

SECTION 5

DIAGRAMS

5-1. EXPLANATION OF IC TERMINALS

IC501 SB662106A-4J90-TLM (BASE UNIT CPU)