SPP-A9171

— 57 —

— 58 —

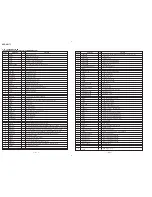

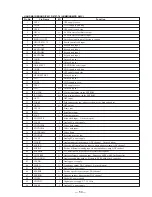

6-12. IC PIN FUNCTIONS

• BASE MAIN BOARD IC501 R6797-76 (HUMMINGBIRD ASIC)

Pin No.

Pin Name

I/O

Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

VSSC

VDDP

VSSP

OSCO

OSCI

RIP/BRANCHP

SW CTL

KEYPADC4

KEYPADC3

TAD REQ

TAQ ACK

ASIC REQ

ASIC ACK

HB-SELECT

VDDP

VSSP

CHG CTL

BATT CHACK

VDDC

VSSC

RING

I2C-CLK

I2C-DATA

ARTI

PARKP

ARTO

FSYNC

SIN

SOUT

CDCMCLK

CAVSS

CDCDATA0

CDCDATA1

CDCFRAME

CDCPOR

CAVSS

LINEIN

MICINN

MICINP

MICBIAS

CDCVREF

CDCAGND

CAVDD

LINEO

CAVSS

SPKROP

SPKRON

CDVSS

CDVDD

CAVSS

–

–

–

O

I

I

I

–

–

I

I

O

O

I

–

–

O

I

–

–

–

O

I/O

I

I

O

–

I

O

–

I

O

I

–

I

I

I

–

–

–

O

O

I

O

I

O

–

I

I

I

VSS supply to core

VDD supply to pad ring

VSS supply to pad ring

9.6 MHz crystal oscillator output

9.6 MHz crystal oscillator input

Detection signal input of the ringer coming

Switch control read input

Not used (open)

Not used (open)

TADµC REC input

TADµC ACK input

ASIC REQ output

ASIC ACK output

HAND/BASE select input

VDD supply to pad ring

VSS supply to pad ring

Charge detection control terminal

Battery voltage detection input terminal

VDD supply to core

VSS supply to core

Signal output of the ringer coming to TAD uc

Clock signal output to the EEPROM

Two-way data bus with the EEPROM

ART input

Park input; active low on base station, active high on handset

ART output

Frame sync

Serial data input

Serial data output

Main clock input

Not used (open)

Analog 0V power supply

Codec data output

Codec data input

Codec frame

Reset input, active low

Analog 0V power supply

Analog input to line pre-amp, ADC channel

Negative differential analog input to microphone pre-amp, ADC channel

Not used (open)

Positive differential analog input to microphone pre-amp, ADC channel

Not used (open)

2.2V nominal DC bias source for electret microphone

Not used (open)

Analog reference voltage output Bypass to AVSS with 0.1uF capacitor

Analog ground bias output Bypass to AVSS with 0.1uF capacitor

Analog power supply

Line driver output, DAC channel

Analog 0V power supply

Positive speaker driver output, DAC channel

Negative speaker driver output, DAC channel

Not used (open)

Digital 0V power supply

Digital power supply, 2.7-5.5 Volts

Analog 0V power supply

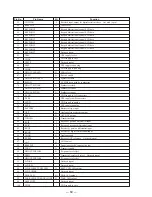

Pin No.

Pin Name

I/O

Function

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

CDCICLK

RESETOP

KEYPADR1

KEYPADR2

KEYPADR3

KEYPADR4

NOMAL/TEST MODE

PAGE

KEYPADC6

TONE/PULSE

VSSC

VDDC

TEST P

VSSP

VDDP

GPIOC1/LNAATN

RXEN

GPIOC6/SYNDATA

REFOSC

GPIOC7/SYNCLK

GPIOC5/SYNSTB

GPIOC4/SYNEN

DVDD

DVSS

AVDD

AVSS

BATTERY

VRP

AUXDAC

TXDATA

RXIP

RXIN

RXQP

RXQN

AGND

RXREF

AGC

RESETIP

TXEN

GPIOC3/TXPWR1

TRSW

GPIOC2/TXPWR0

DATA BUSS 0

DATA BUSS 1

DATA BUSS 2

DATA BUSS 3

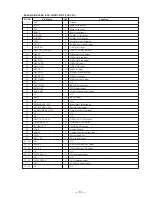

MITEL FSKEN

MITEL STD

OHP

VDDC

–

O

–

I

I

–

–

O

–

I

–

–

–

–

–

O

O

O

–

O

O

O

–

–

–

–

I

O

–

O

I

I

I

I

O

–

O

I

O

O

O

O

I/O

I/O

I/O

I/O

–

I/O

O

–

Bit clock input/output for digital serial interface

Not used (open)

Codec reset

Not used (open)

Dial mode switch input terminal

Dial mode switch input terminal

Not used (open)

TEST MODE terminal

Not used (open)

Not used

Dial mode switch input terminal

VSS supply to core

VDD supply to core

Not used (open)

VSS supply to pad ring

VDD supply to pad ring

LNA select

Receive enable

Synthesizer data

9.6 MHz clock used by synthesizer

Synthesizer clock

Synthesizer strobe

Synthesizer power

VDD supply to A/D converters

VSS supply to A/D converters

VDD supply to analog

VSS supply to analog

Battery voltage input

Analog voltage reference output

AFC DAC output

Not used (open)

Transmitter data

Receiver I positive differential input

Receiver I negative differential input

Receiver Q positive differential input

Receiver Q negative differential input

Analog ground

Receiver ADC reference

Not used (open)

AGC control

Power-on reset RC input; active low

Transmit enable

PA power level select

Transmit=1/receive=0 select

Not used (open)

PA power level select

TADµC

↔

ASIC DATA BUSS

TADµC

↔

ASIC DATA BUSS

TADµC

↔

ASIC DATA BUSS

TADµC

↔

ASIC DATA BUSS

Not used (open)

Not used (open)

Hook on/off control signal output terminal

VDD supply to core